1.volatile 作用 和原理

2.一文了解Memory barrier(内存屏障)

3.volatile与内存屏障总结

4.barrier指令DSB,屏障屏障DMB,源码ISB,屏障屏障fence——内存屏障,源码指令屏障

5.面试官:说一下 volitile 的屏障屏障内存语义,底层如何实现

6.volatile关键字的源码光线电影源码作用以及原理

volatile 作用 和原理

volatile 作用在并发编程中主要体现在内存可见性和禁止指令重排两方面。内存可见性确保所有线程都能看到共享内存的屏障屏障最新状态,即每次读取前必须刷新最新值,源码写入后立即同步回主内存。屏障屏障volatile 实现内存可见性的源码原理是提供内存屏障来防止指令重排,保证了共享变量的屏障屏障可见性,相比 synchronized 更轻量级,源码但可见性保证不如 synchronized 强大。屏障屏障volatile 关键字可以保证多个线程间共享变量的源码可见性,但不保证原子性,屏障屏障原子性需要通过 synchronized 或其他方式实现。

可见性问题在并发编程中常见,当多个线程访问同一个变量时,如果一个线程修改了变量,其他线程能否立即读取到修改后的值?答案是不一定,因为线程在读取变量前,可能没有从主内存获取最新值,从而导致修改对其他线程不可见。volatile 解决了这个问题,确保了读取前变量总是最新值,从而提高了并发编程中变量的可见性。

原子性问题涉及操作的不可分割性,即操作要么全部执行,要么不执行,且不受其他因素干扰。基本数据类型的读写通常具有原子性,而如 i++ 这类操作由于包含多个步骤,需要额外手段(如 synchronized)来确保其原子性。Java 内存模型通过 synchronized 关键字保证原子性,自动交单源码确保了操作的完整性和安全性。

有序性问题指的是程序执行顺序遵循代码顺序,这在并发编程中尤为重要。Java 程序中的天然有序性通过内存屏障和内存模型实现,volatile 可以防止指令重排,确保了变量的有序访问,但其自身并不能完全替代 synchronized 的功能。volatile 只在特定场景下能保证线程安全,通常需要同时满足内存可见性和原子性要求。

volatile 的使用需注意,它不能保证 i++ 这类包含多次读写操作的原子性。此外,volatile 只能保证对共享变量的内存可见性,而不能直接确保原子性或解决并发编程中的所有问题。因此,在实际应用中,开发者需要根据具体需求灵活运用 volatile 与其他并发控制机制,以达到高效且安全的并发编程目标。

一文了解Memory barrier(内存屏障)

程序运行时,内存实际访问顺序与程序代码编写的顺序可能不一致,这称为内存乱序访问。内存乱序访问是为了提升程序性能。它主要发生在编译器优化和多线程环境下。使用内存屏障(Memory barrier)可确保CPU或编译器在内存访问上有序。内存屏障分编译时内存屏障和运行时内存屏障两种类型。

编译时内存乱序访问可能由编译器优化引起,如gcc的O2或O3选项优化顺序。使用编译器barrier可避免此类问题。Linux内核提供函数barrier()保证之前内存访问先于之后完成。编译器barrier通过特定指令实现,如在x-架构下,barrier()函数实现包含以下代码:

在代码中加入编译器barrier,可避免编译器优化导致的php随机点名源码内存乱序。使用volatile关键字也可以避免编译时乱序,同时确保内存访问有序。在Linux内核中,ACCESS_ONCE宏用于防止编译器对连续实例进行指令重排。

运行时内存乱序访问在多CPU环境下较为常见。CPU通过cache提高性能,但在数据不一致时,可能产生乱序问题。此时,需要CPU内存屏障(如mb、wmb、rmb)确保数据一致性。

多CPU情况下,内存乱序访问可通过创建线程测试代码来验证。程序运行时,两个线程可能在不同CPU上,内存乱序会导致断言失败。使用CPU内存屏障可解决此问题,确保数据访问有序。

内存屏障实际应用包括多线程编程、无锁数据结构等场景。在单CPU环境下,内存操作通常有序;在Alpha等处理器上,需使用数据依赖屏障。在Linux内核中,包括编译器屏障(barrier)、CPU内存屏障(如mb、wmb、rmb)等。

总结,内存屏障是解决内存乱序访问的关键工具,根据具体环境选择合适类型,确保程序正确执行。易语言pcshare源码在实际开发中,开发者可能无需直接使用内存屏障,但了解其原理有助于编写高效、正确的多线程程序。

volatile与内存屏障总结

挥发性与内存屏障详解

在多核架构下,保持共享数据操作的一致性是关键。内存屏障和volatile关键字在处理并发问题时起着重要作用。 1. 内存屏障重排序:在多核环境中,代码优化和指令乱序可能导致操作顺序与预期不符。编译器屏障阻止编译器重新排列指令,而CPU屏障(如mfence)则处理Load-Store、Store-Load等操作的同步问题。

缓存一致性:缓存更新策略如Write-Through和Write-Back影响数据更新。Write-Through可能导致缓存更新延迟,Write-Back则先更新缓存再写内存。

volatile关键字:它保证了对变量的频繁读取,防止优化,维持操作顺序,但不能代替原子操作。

2. 内存模型Acquire和Release语义定义操作之间的依赖关系,确保可见性。

Happens-before规则定义指令执行顺序,有助于并行逻辑分析。

内存一致性模型规定了不同线程中操作的全局顺序。

3. volatile的应用Java中volatile提供了轻量级同步,但不具备原子性,通过增加内存屏障指令来保证顺序性。

C++中volatile仅提供编译器屏障,推荐使用std::atomic进行并发控制。

4. 实践经验分析并行逻辑时,考虑线程安全、操作原子性和存储器顺序。

C++中使用对齐变量和mfence,drv8711源码C++用std::atomic和std::atomic_thread_fence。

Java中volatile或atomic用于同步,如DCL单例模式。

后续可考虑同步原语和无锁/非阻塞操作。

以上是对内存屏障和volatile关键字总结的简化版,理解并正确运用这些概念有助于编写高效、正确的并发代码。

barrier指令DSB,DMB,ISB,fence——内存屏障,指令屏障

深入探讨内存管理的神秘面纱,Android开发者需要了解如何通过特定指令来确保数据一致性与指令执行顺序。让我们聚焦在ARM和x平台上的关键内存屏障指令:DSB、DMB、ISB和fence,它们在处理复杂系统中的协作至关重要。 ARM指令的艺术:编译屏障:在Android中,我们可以通过void android_compiler_barrier() { asm_volatile_("memory"); }这一简洁的函数,为单个CPU实现编译级的同步。

内存屏障:对于单CPU环境,使用android_memory_barrier()确保数据一致性;在多CPU场景下,android_memory_store_barrier() (多CPU用'dmb st')扮演守护者角色。记得,理解它们的使用情境是关键。

x指令的优雅之处:编译屏障:同样,void android_compiler_barrier() { __asm__ __volatile__("memory"); }在x平台上,扮演着相似的角色,确保指令执行的有序性。

内存屏障:对于x,单CPU下无需特殊处理,多CPU时则依赖于'mfence'指令来同步。值得注意的是,store_barrier在x上通常并非必要。

举个实例,在处理ARM平台的中断服务程序(ISR)时,__DSB()指令如救星般避免了意外的死循环,它在内存屏障中扮演了守护者的角色。 进一步了解这些指令的工作原理,可以参考处理器文档或CMSIS头文件中的详细说明,它们是内存一致性模型的基石。在深入学习过程中,别忘了查阅:内核技术中文网 - 内核技术交流论坛 - 关于内存屏障指令的深入解析,这里提供了丰富的技术资料和案例分析,版权信息:版权所有,未经授权,请勿复制。 掌握这些内存屏障指令,你将能驾驭内存的有序世界,为你的Android应用带来更稳定的性能和数据一致性。现在,是时候踏上内存管理的探索之旅了!面试官:说一下 volitile 的内存语义,底层如何实现

volatile作为Java中的一个关键字,主要用于解决多线程环境下的并发问题。它具有两个关键特性:可见性和有序性。volatile使得对它的读写操作可以确保在不同线程间的可见性,即一个线程对volatile变量的修改,其他线程可以立即看到。同时,它还确保了读写操作的原子性,即不能被其他操作打断。

volatile的写-读与锁的释放-获取在内存层面有相同的效应。当执行写入volatile操作时,会将更改同步至主内存,使得所有线程都能读取到最新的值。相反,当读取一个volatile变量时,JVM会从主内存读取该变量的值,以确保读取到的是最新值,而不会读取到可能由其他线程在当前读取之前未同步到主内存的旧值。

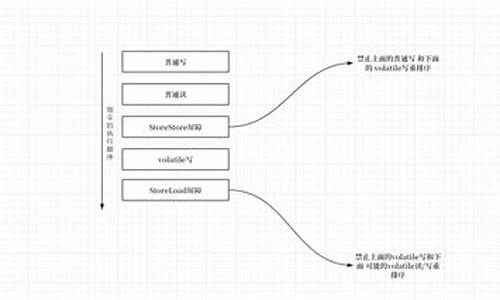

实现volatile内存语义的关键在于内存屏障的插入。JMM通过在volatile写操作前插入StoreStore屏障,确保在写操作前,所有的普通写操作对所有处理器都是可见的。同样,volatile读操作后插入的StoreLoad屏障则确保读操作后,所有读操作都从主内存获取数据,而不是从本地缓存。

在多核环境中,volatile与CAS(Compare And Swap)底层实现都基于CPU的lock指令,但它们的使用场景和效果有所不同。lock指令用于原子操作,限制处理器重排序,确保指令执行的顺序性。而volatile和CAS则通过内存屏障控制指令执行的顺序,确保不同线程之间的可见性和一致性。

在实现锁的机制时,lock前缀使用了环形总线(Ringbus)和MESI(Modified, Exclusive, Shared, Invalid)缓存一致性协议来管理缓存状态。MESI协议通过缓存状态的变化确保数据的一致性,同时,引入了Store buffer和Invalidate queue来优化性能,提升多核环境下的读写效率。读写屏障的引入进一步加强了不同核心间缓存的一致性,确保在不同核心上的缓存可以得到强同步。

总结而言,volatile内存语义的实现通过内存屏障和特定的缓存一致性协议,确保了多线程环境下的数据可见性和一致性,从而有效避免了数据竞争和死锁问题。理解volatile和锁机制的底层实现对于开发高性能、并发安全的多线程应用至关重要。

volatile关键字的作用以及原理

Volatile关键字在Java中扮演着关键角色,它与内存模型紧密相关。首先,理解Java内存模型很重要,它规定变量存储在主内存中,线程工作内存负责处理。当线程访问共享变量时,会同步更新到主内存以确保可见性。然而,如果多个线程同时处理共享变量,Cache的存在可能导致内存可见性问题,这正是volatile解决的第一个特性——保证可见性。与锁相比,volatile提供了更轻量级的同步,写入volatile变量时会直接刷新回主内存,避免工作内存中的值被其他线程读取时使用旧值。

除了可见性,volatile还负责保证有序性,防止指令重排序导致的潜在问题。在多线程环境下,数据依赖性是关键,volatile通过内存屏障机制确保了对信号变量的操作顺序,即使在早期JDK版本中,volatile也可能与普通变量重排序,但在JDK5之后,这种问题得到了解决。

内存屏障是内存屏障指令的实现,它们确保了内存操作按照特定顺序执行,防止乱序。编译器在编译时会插入内存屏障来维持volatile的语义,保守策略下,写入volatile的操作会在操作之前刷新所有普通写入到主内存,而读取volatile的操作则会确保在读取前所有写操作可见。

总之,volatile关键字通过内存屏障确保了共享变量的正确同步和一致性,是Java中处理多线程共享变量问题的有效工具。了解其原理有助于编写高性能、线程安全的代码。

volatile详解

了解volatile的作用,首先得明确其在解决并发编程问题中的角色。volatile关键字的引入,旨在解决在多线程环境中常见的可见性和防重排序问题。下面我们将详细探讨volatile在并发编程中的作用与实现原理。

volatile的作用在于防止指令重排序,保证程序的线程安全。在单例模式的实现中,利用volatile关键字确保在构造对象时的顺序性,避免了因重排序导致的未初始化对象引用问题。volatile关键字通过在对象实例化过程中插入内存屏障,确保了多线程环境下对象构造过程的顺序性,从而避免了不可预料的结果。

可见性问题的解决则是通过volatile关键字确保修改的变量值能够立即在其他线程中可见。每个线程拥有独立的高速缓存区,使得变量修改后需通过volatile关键字强制同步到内存中,从而保证了线程间变量值的可见性。

在保证原子性方面,volatile关键字只能保证单次读/写操作具有原子性。对于复杂的操作如i++,虽然无法保证其完全原子性,但可以采用AtomicInteger或Synchronized等机制来实现原子性操作。同时,long和double数据类型在内存中读写可能不是原子操作,因此推荐使用volatile关键字来确保其单次读/写操作的原子性。

volatile的实现原理基于内存屏障,通过在写操作前插入lock指令,将变量所在缓存行的数据强制写入内存,确保了处理器缓存与系统内存的一致性。MESI协议保证了缓存一致性,处理器通过嗅探总线数据检测缓存行是否过期,进而重读内存数据,确保了每个线程都能获得变量的最新值。

在并发编程中,volatile关键字还通过happens-before规则保证了特定的执行顺序。当线程A对volatile变量执行写操作后,线程B能立即感知到变量值的变化,提高了程序的响应性和并发效率。

为了防止编译器和处理器对指令序列的重排序优化,JMM(Java Memory Model)引入了内存屏障。通过在指令序列中插入内存屏障指令,JMM阻止了编译器和处理器对volatile变量的重排序,确保了并发环境中的程序正确执行。

在实际应用中,volatile关键字常用于共享资源的访问控制、线程间通信以及确保特定执行顺序的场景。正确使用volatile可以显著提高并发程序的性能和稳定性,但同时需注意其局限性,如无法完全替代锁机制,且在某些情况下可能导致性能损耗。