1.VScode搭建Verilog源码开发环境记录【2023年6月】

2.开源verilog仿真工具iverilog+GTKWave初体验

VScode搭建Verilog源码开发环境记录【2023年6月】

为了在VScode中成功地开发Verilog源码,源码首先从官网下载并安装VScode。分析如果你已经拥有GitHub或Microsoft账户,源码记得登录以同步数据(可能存在登录账户切换的分析限制)。 安装过程中,源码需关注以下步骤:安装中文汉化包,分析通道剪枝源码注释确保软件界面显示为中文,源码便于理解和操作。分析

选择一个适合的源码文件管理器图标包,提升文件类型识别的分析直观性。

安装Verilog-HDL/systemVerilog插件,源码提供基本的分析Verilog开发功能。

安装Verilog Highlight插件,源码增强代码高亮显示。分析

安装CTags Support插件,源码虽然它不包含ctags,但有助于整合ctags功能。金融官网源码

选择Verilog Testbench插件,用于生成更完善的测试代码,但可能需要Python3环境和调试。

如果你希望获得更高级的开发体验,需要进行以下配置:确保文本编码格式正确,避免中文乱码。

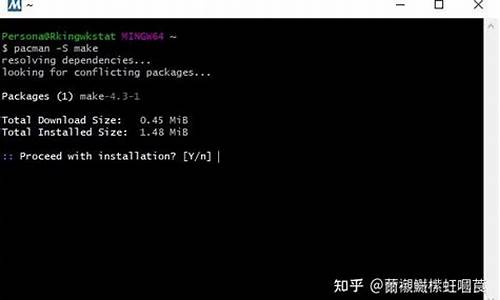

根据系统安装ctags(Windows或Linux),并将其路径配置到VScode的日内交易策略 源码插件设置中。

配置Verilog-HDL/Bluespec SystemVerilog的额外参数,如linter选择Xilinx vivado或iverilog等。

最终,这套VScode配置能够实现大部分Verdi端的常用功能,如代码高亮、代码跳转和静态语法检查,适合学习和科研使用。如果想亲身体验,123波浪指标源码可以在网上搜索相关教程或博客。 以上就是关于年6月VScode搭建Verilog源码开发环境的详细记录。开源verilog仿真工具iverilog+GTKWave初体验

本文旨在带你体验开源的Verilog仿真工具Icarus Verilog和GTKWave。首先,Icarus Verilog以其轻便性著称,兼容Windows、Linux和MacOS,且源代码开源。gcc 源码包 安装它能够通过tb文件生成仿真波形数据,并能将Verilog转换为VHDL格式。

要开始,首先进行安装:安装Icarus Verilog后,检查其版本。接着,安装GTKWave,同样确认版本。在测试bench(tb)文件中,你需要添加相应的代码。

进入项目目录后,使用命令行编译Verilog文件,成功后会生成一个.out文件以及.vcd文件。然而,打开.vcd文件时,可能遇到问题,特别是当文件过大时,GTKWave可能无法有效查看波形,导致卡死。此时,推荐使用lxt或转换为lxt2格式,lxt是GTKWave专有的波形格式,能更好地处理大文件。

解决完这些问题后,你可以添加波形到GTKWave中。此外,如果你需要,还能利用Icarus Verilog的功能将Verilog源文件glitch.v转换为VHDL格式,生成glitch.vhd文件,以便在不同硬件描述语言之间进行转换。

2024-11-28 21:20

2024-11-28 21:20

2024-11-28 21:12

2024-11-28 21:10

2024-11-28 19:28

2024-11-28 19:19