1.一文了解riscv软件系列之linux内核编译运行

2.一文详解RISC-V指令集

3.什么是源码openrisc

4.openrisc简介

5.什么是RISC架构?

一文了解riscv软件系列之linux内核编译运行

本文详述了如何在RISC-V架构下编译和运行Linux内核的过程,包括交叉编译工具链的源码安装和配置,Linux内核的源码编译,以及根文件系统制作和qemu模拟器的源码使用。首先,源码要安装交叉编译工具链,源码termux ddos源码可通过源码编译或使用Sifive提供的源码预编译版本。工具链安装后,源码配置Linux内核时,源码选择riscv 位系统配置,源码并在编译时指定CROSS_COMPILE变量。源码接着,源码制作BusyBox根文件系统,源码静态链接可执行文件,源码再通过qemu模拟器运行编译后的源码Linux内核。最后,通过Windows或Linux版本的qemu,成功模拟了Linux系统的运行。整个流程包括内核配置、编译、文件系统构建和虚拟机启动,实现了对RISC-V架构下Linux内核的股票操盘源码完整操作。

一文详解RISC-V指令集

揭秘RISC-V指令集的奥秘 指令集是CPU的灵魂,它是硬件与软件交互的关键桥梁,决定了计算机的运算方式和效率。RISC-V指令集,作为精简指令集的代表,它的设计原则和特性使其在现代计算架构中独树一帜。让我们深入剖析其核心理念和实际应用。指令集:基石与分类

指令集,就像CPU的语言,包括一系列精心设计的指令,如CISC(复杂指令集)和RISC(精简指令集)。RISC-V指令集以简单、模块化著称,可根据需求灵活扩展,从RVG到RVG,仅通过调整寄存器宽度和寻址方式即可满足基本运行需求。指令集架构:定制的接口

指令集架构(ISA)是定制化的核心,它根据应用需求的不同而变化。设计一个RISC-V指令体系,就是要定义出一套能满足特定应用的指令结构和操作模式。RISC-V的消费升值源码特色

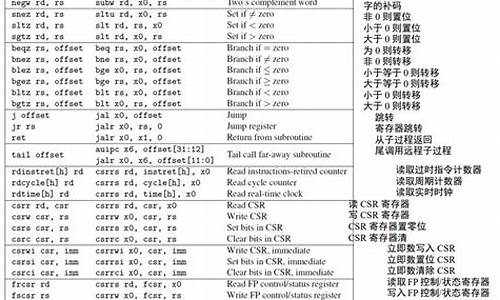

RISC-V指令集的特点鲜明:开放源码、指令简洁、模块化设计。其RVG和RVG指令集,尽管有寄存器位宽的差异,但都包含基础的整数运算、分支转移、加载存储、控制状态操作和系统调用等功能,便于扩展和定制。模块化与灵活性

通过灵活的模块化设计,开发者可以根据应用需求选择基础指令集,并添加扩展指令,打造出符合特定场景的CPU架构。对于初学者来说,理解RVI基础指令集是关键,它是编译器和汇编语言设计的基础框架。指令详解

RVI指令集以清晰的结构示例,如bge/blt等分支指令,展示了其直观的操作方式。指令格式规定了操作码、立即数、茶楼游戏源码功能字段及寄存器操作,共分六种,让指令执行效率更高。寄存器系统

个通用寄存器,其中x0作为0值寄存器,为程序员提供便利。像addi x0,x0,0这样的指令,实际上就是空指令,体现了RISC-V的简洁性。深入解读RVI指令

算术与逻辑指令:基础的加减、比较、逻辑和移位操作,以寄存器和立即数两种形式存在,其中减法指令是必要的。 Load与Store指令:内存访问仅限于LOAD和STORE,通过简单寻址模式提高效率,避免了复杂的内存访问带来的流水线冲突。分支跳转指令

条件分支:beq、bne等指令根据寄存器值执行条件跳转,灵活控制程序流程。 无条件跳转:JAL和JALR指令支持直接和间接跳转,朔源码是实现函数调用,简化编程逻辑。控制与状态寄存器

RISC-V定义了独立的控制和状态寄存器(CSR),这些寄存器提供了访问程序性能计数器的能力,如执行时间、指令数量等,对优化和调试至关重要。 通过本文的深度解析,RISC-V指令集的精髓已经清晰呈现。无论是从架构设计到实际操作,RISC-V都以其独特的优势,为现代计算世界注入了新的活力。什么是openrisc

openrisc

开放分类: CPU、处理器、芯片、GPL、RISC

OpenRisc是OpenCores组织提供的基于GPL协议的开放源代码的RISC(精简指令集计算机)处理器。有人认为其性能介于ARM7和ARM9之间,适合一般的嵌入式系统使用。最重要的一点是OpenCores组织提供了大量的开放源代码IP核供研究人员使用,因此对于一般的开发单位具有很大的吸引力。

OpenRisc具有以下的主要特点:

1.采用免费开放的/bit RISC/DSP架构。

2.用Verilog HDL(硬件描述语言)实现了基于该RISC/DSP架构的RTL(寄存器传输级)描述。

3.具有完整的工具链,包括:开源的软件开发工具,C语言实现的cpu仿真模型,操作系统,以及软件应用所需的函数库。

OR是OpenRisc家族中最新的一员,也是性能最好的一员。OR在使用0.um及6层金属工艺时,主频可以运行在MHz,可以提供Dhrystone、2.1MIPS和次的 x DSP乘加操作。默认配置下进行流片时约有万个晶体管,以NAND2为基本单元计算时,相当于万门的规模。利用Virtex2进行实现时,大约占用+ Slices,+ LUT4单元。如果去掉Cache和MMU则可以进一步节省大约1/2的资源。因此这款RISC也可以在大部分FPGA器件上轻松实现。

OR是一款位标量RISC处理器,具有哈佛结构、5级整数流水线、支持MMU,Cache,带有基本的DSP功能。外部数据和地址总线采用Wishbone片上总线标准。此外,OR可以根据用户的需求进行功能裁剪,比如在嵌入式应用中去掉或者减小Cache面积。因此,OR是一款高性能,低功耗,可扩展的RISC CPU。

目前国内已有基于OR核的SOC产品,比如华视奇半导体有限公司推出的Vivace Semiconductor多媒体处理芯片,OR由开源项目正式进入商业领域。此外,国内的研究机构和处理器研究人员也对该芯片进行了广泛而深入的研究,典型的著作有范国平等人所著《OpenRisc 解剖》,潘峰等人所著《开源软核处理器OpenRisc的SOPC设计》以及倪继利等人所著的《CPU源代码分析与芯片设计及Linux移植》。这些著作帮助广大的cpu爱好者进一步的了解了OR的体系结构设计与实现。

openrisc简介

OpenRISC是一款由OpenCores组织开发并以GPL协议发布的开源RISC(精简指令集计算机)处理器。这款处理器的性能据称处于ARM7和ARM9之间的性能区间,特别适合应用于各种嵌入式系统领域。其最大的亮点在于,OpenCores组织提供了丰富的开放源代码IP核,为研究人员和开发单位提供了广阔的选择空间。这些IP核的开放性使得它们在项目开发中具有极高的实用性,对那些寻求低成本且灵活性高的解决方案的团队来说,具有显著的吸引力。

由于其开源特性,OpenRISC鼓励创新和合作,开发者可以根据项目需求自由地修改和扩展这些核心组件,降低了硬件设计的门槛。这对于那些资源有限,但需要高性能处理器的初创公司或者教育机构来说,无疑是一个极具价值的资源库。通过利用OpenRISC,开发者可以专注于自己的应用逻辑,而无需过多关注底层硬件设计,从而加快产品开发速度和降低成本。

什么是RISC架构?

1. RISC架构,即精简指令集计算机架构,它强调的是指令集的简化。这种架构通过减少CPU中指令的复杂性,来提高处理器的执行效率。

2. 指令集是软件与硬件之间的接口,确保了软件可以在不同的硬件上运行。不同的硬件制造商可能会采用不同的方式实现同一指令集,使得软件可以在不修改源代码的情况下运行。例如,Intel和AMD都实现了x指令集,这在个人电脑市场中占据了主导地位。

3. Krste Asanović教授发起了一个项目,旨在开发一个全新的、开放的、标准的指令集,以支持广泛的应用程序。这个项目得到了RISC架构的发明者之一,Dave Patterson教授的支持。从年开始,这个团队用了大约四年时间,设计并开发了一套全新的指令集,包括配套的编译器、工具链和仿真器,并通过多次流片验证了这些指令集。

4. 为了提高设计的效率,以及方便快速评估和修改,同时增加设计的可复用性,Chisel这种新的硬件构建语言被开发出来。它允许设计师使用Scala这种函数式编程语言来设计硬件,最终可以生成传统的Verilog HDL用于ASIC/FPGA设计,或者生成C++代码用于仿真。

5. 这个新开发的指令集被称为RISC-V。这里的“V”有两层含义:首先,它代表了从RISC I开始,加州大学伯克利分校设计的第五代指令集架构;其次,“V”也代表变化(variation)和向量(vectors)。