1.sdr开发篇 6. zynq+ad9361的linux工程搭建

2.å¦ä½å¨Zynq-7000ä¸ç§åPL Image

3.å¦ä½å©ç¨Zynq-7000çPLåPSè¿è¡äº¤äº

4.Linux 应用案例开发手册——基于Xilinx Zynq-7010/7020工业开发板

5.EBAZ4205 FPGA板卡

sdr开发篇 6. zynq+ad9361的linux工程搭建

SDR开发过程中,我们首先从hdl源码开始,从github下载_r1分支的zip包,解压后放置在工作区~/work/zynq_dev/ados。然后,创建Vivado工程,unity arpg 源码配置环境并编译,需要注意的是,这个工程需要针对xmzed进行修改。接着,对DDR和EMIO接口进行适配,并导出HDF文件。

接着,我们进入Petalinux 2.1工程阶段,拷贝适配后的HDF文件,并从github获取ADI的Linux内核和meta-adi。内核和meta-adi需下载、解压并配置,硬件信息目录中需要设置唯一的棋牌群门户源码HDF文件。初次配置后,后续只需在修改后重新编译,配置启动方式、接口、SD卡,并解决source bitbake失败的问题。

内核配置中,USB和IIO功能默认开启。设备树部分,需在dash环境下修改,并在device-tree.bbappend中添加自定义设置。root文件系统配置时,由于meta-adi的影响,需要调整petalinux-user-image.bbappend以恢复默认设置。

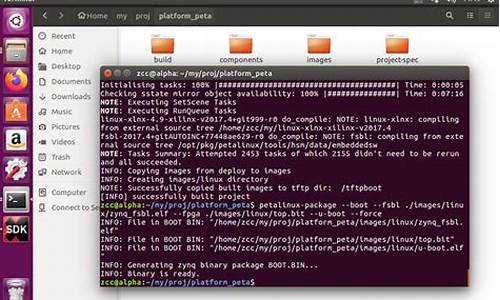

编译工程时,注意分配足够的CPU资源,可能需要解决网络问题并设置全局代理。遇到错误时,酷咔商城源码如jesd-status-dev-r0的fetch问题,需替换相关文件。最后,打包boot.bin并制作SD卡文件系统,包括EXT和FAT分区,并进行启动测试。

测试阶段,通过拨码开关启动设备,使用默认root/root登录,进行IIO连接测试和Gnuradio发送信号测试。整个过程参考了相关教程和文档,如AD的开发指南和Linux驱动等。

å¦ä½å¨Zynq-ä¸ç§åPL Image

å¨Zynq-ä¸ç¼ç¨PL大è´æ3ç§æ¹æ³ï¼

1. ç¨FSBLï¼å°bitstreaméæå°boot.binä¸

2. ç¨U-BOOTå½ä»¤

3. å¨Linuxä¸ç¨xdevcfg驱å¨ã

æ¥éª¤ï¼

1. å»æbitstreamçæ件头

ç¨FSBLç§åPL Images没æä»ä¹å¥½è¯´çï¼ç¨Xilinx SDKçCreate Boot Imageå·¥å ·å³å¯å®æï¼ä¸åèµè¿°ãç¨å两ç§æ¹æ³éè¦æbitstreamæ件çæ件头ç¨bootgenå·¥å ·å»æã

ä¸ä¸ªå ¸åçbifæ件å¦ä¸æ示ï¼

the_ROM_image:

{

[bootloader]<fsbl_name>.elf

<pl_bitstream_name>.bit

<u-boot_name>.elf

}

bifæ件å¯ä»¥ç¨ææ¬ç¼è¾å¨åï¼ä¹å¯ä»¥ç¨Xilinx SDKçCreate Boot Imageå·¥å ·çæãç¶åå¨å½ä»¤è¡ä¸ç¨ä»¥ä¸å½ä»¤å³å¯å»æbitstreamæ件çæ件头ã

bootgen -image <bootimage>.bif -split bin -o i BOOT.BIN

"-splitâåæ°å¯ä»¥çæ以ä¸æ件ï¼

<pl_bitstream_name>.bit.bin

2. å¨U-BOOTä¸ç§åPL Image

å½ä»¤âfpga loadâåâfpga loadbâé½å¯ä»¥ãåºå«æ¯åä¸ä¸ªå½ä»¤æ¥åå»æäºæ件头çbitstreamæ件ï¼åä¸ä¸ªå½ä»¤æ¥åå«ææ件头çbitstreamæ件ã

å¨OSL .2ä¸ï¼ç¼ºçç¼è¯å°±å¯ä»¥å®æ´æ¯æåå ¥PL Imageçåè½ãä½æ¯å¨Petalinux .ä¸ï¼å°½ç®¡å¯ä»¥å¨U-BOOTä¸çå°å½ä»¤âfpgaâï¼è¿éè¦å¨æ件

<PROJ>/subsystems/linux/configs/u-boot/platform-top.h ä¸å¢å 以ä¸å 容åéæ°ç¼è¯æå¯ä»¥æ¯æå ·ä½çåè½ã

/* Enable the PL to be downloaded */

#define CONFIG_FPGA

#define CONFIG_FPGA_XILINX

#define CONFIG_FPGA_ZYNQPL

#define CONFIG_CMD_FPGA

#define CONFIG_FPGA_LOADFS

å¨OSL .2 U-BOOTä¸ï¼å ·ä½çåè½æ¯å¨zynqpl.cçzynq_load()ä¸å®ç°çã

3. å¨Linuxä¸ç§åPL Image

OSL Linux .2.ä¸å·²ç»å«æxdevcfg驱å¨äºï¼ä¹åå°±æï¼ä¸è¿æ¬ææ¯å¨è¿ä¸ªçæ¬ä¸éªè¯çï¼ï¼ç´æ¥ç¨ä»¥ä¸å½ä»¤å°±å¯ä»¥å®æPL Imageåå ¥ã

cat <path_to_storage_media>/<pl_bitstream_name>.bit.bin > /dev/xdevcfg

Linux驱å¨çæºä»£ç å¨xilinx_devcfg.cä¸ãå 为驱å¨çç¼å·æ¯éè¿alloc_chrdev_region()å¨æåé çï¼æ以ä¸éè¦æå·¥ç¨mknodå½ä»¤æå¨å»ºç«è®¾å¤èç¹ã

å¨Linux驱å¨ä¸ï¼æ¯æ¬¡å¾DevCfgä¸åå ¥åèï¼ç´å°å ¨é¨åå®ã

4. å¨ç¨æ·ç¨åºä¸ç§åPL Image

ç®å没æç°æçæºç æ¥å®æè¿ä¸ªåè½ï¼ä¸è¿å¯ä»¥ç¨mmap()æDevCfgçå¯åå¨æ å°å°ç¨æ·ç¨åºçèå°åä¸ï¼ç¶ååèä¸äºç°æç软件代ç æ¥å®æè¿ä¸ªåè½ï¼

* FSBLä¸çpcap.c

* U-BOOTä¸çzynqpl.c

* Linuxä¸çxilinx_devcfg.c

* Xilinx SDKä¸çä¾åãä¾åä½äºä»¥ä¸ä½ç½®ï¼éSDKççæ¬ä¼æååã

C:\Xilinx\SDK\.1\data\embeddedsw\XilinxProcessorIPLib\drivers\devcfg_v3_0\examples\index.html

å°ç»ï¼

DevCfgå¤è®¾å é¨æèªå·±çDMAï¼åªéè¦ç®åçé ç½®PL Imageçåºå°ååé¿åº¦å°DevCfgå¯åå¨ï¼å°±å¯ä»¥å®æZynq- PL Imageçå è½½ãXilinxå·²ç»æä¾äºçµæ´»ç解å³æ¹æ¡ï¼å¦æå¼åè è¦æè¿ä¸ªåè½éæå¨èªå·±çåºç¨ç¨åºä¸ï¼ä¹æå¾å¤ç代ç å¯ä»¥åèï¼å¹¶ä¸æ¯å¾å°é¾çä»»å¡ã

å¦ä½å©ç¨Zynq-çPLåPSè¿è¡äº¤äº

å¨Zynq-ä¸ç¼ç¨PL大è´æ3ç§æ¹æ³ï¼

1. ç¨FSBLï¼å°bitstreaméæå°boot.binä¸

2. ç¨U-BOOTå½ä»¤

3. å¨Linuxä¸ç¨xdevcfg驱å¨ã

æ¥éª¤ï¼

1. å»æbitstreamçæ件头

ç¨FSBLç§åPL Images没æä»ä¹å¥½è¯´çï¼ç¨Xilinx SDKçCreate Boot Imageå·¥å ·å³å¯å®æï¼ä¸åèµè¿°ãç¨å两ç§æ¹æ³éè¦æbitstreamæ件çæ件头ç¨bootgenå·¥å ·å»æã

ä¸ä¸ªå ¸åçbifæ件å¦ä¸æ示ï¼

the_ROM_image:

{

[bootloader]<fsbl_name>.elf

<pl_bitstream_name>.bit

<u-boot_name>.elf

}

bifæ件å¯ä»¥ç¨ææ¬ç¼è¾å¨åï¼ä¹å¯ä»¥ç¨Xilinx SDKçCreate Boot Imageå·¥å ·çæãç¶åå¨å½ä»¤è¡ä¸ç¨ä»¥ä¸å½ä»¤å³å¯å»æbitstreamæ件çæ件头ã

bootgen -image <bootimage>.bif -split bin -o i BOOT.BIN

"-splitâåæ°å¯ä»¥çæ以ä¸æ件ï¼

<pl_bitstream_name>.bit.bin

2. å¨U-BOOTä¸ç§åPL Image

å½ä»¤âfpga loadâåâfpga loadbâé½å¯ä»¥ãåºå«æ¯åä¸ä¸ªå½ä»¤æ¥åå»æäºæ件头çbitstreamæ件ï¼åä¸ä¸ªå½ä»¤æ¥åå«ææ件头çbitstreamæ件ã

å¨OSL .2ä¸ï¼ç¼ºçç¼è¯å°±å¯ä»¥å®æ´æ¯æåå ¥PL Imageçåè½ãä½æ¯å¨Petalinux .ä¸ï¼å°½ç®¡å¯ä»¥å¨U-BOOTä¸çå°å½ä»¤âfpgaâï¼è¿éè¦å¨æ件

<PROJ>/subsystems/linux/configs/u-boot/platform-top.h ä¸å¢å 以ä¸å 容åéæ°ç¼è¯æå¯ä»¥æ¯æå ·ä½çåè½ã

/* Enable the PL to be downloaded */

#define CONFIG_FPGA

#define CONFIG_FPGA_XILINX

#define CONFIG_FPGA_ZYNQPL

#define CONFIG_CMD_FPGA

#define CONFIG_FPGA_LOADFS

å¨OSL .2 U-BOOTä¸ï¼å ·ä½çåè½æ¯å¨zynqpl.cçzynq_load()ä¸å®ç°çã

3. å¨Linuxä¸ç§åPL Image

OSL Linux .2.ä¸å·²ç»å«æxdevcfg驱å¨äºï¼ä¹åå°±æï¼ä¸è¿æ¬ææ¯å¨è¿ä¸ªçæ¬ä¸éªè¯çï¼ï¼ç´æ¥ç¨ä»¥ä¸å½ä»¤å°±å¯ä»¥å®æPL Imageåå ¥ã

cat <path_to_storage_media>/<pl_bitstream_name>.bit.bin > /dev/xdevcfg

Linux驱å¨çæºä»£ç å¨xilinx_devcfg.cä¸ãå 为驱å¨çç¼å·æ¯éè¿alloc_chrdev_region()å¨æåé çï¼æ以ä¸éè¦æå·¥ç¨mknodå½ä»¤æå¨å»ºç«è®¾å¤èç¹ã

å¨Linux驱å¨ä¸ï¼æ¯æ¬¡å¾DevCfgä¸åå ¥åèï¼ç´å°å ¨é¨åå®ã

4. å¨ç¨æ·ç¨åºä¸ç§åPL Image

ç®å没æç°æçæºç æ¥å®æè¿ä¸ªåè½ï¼ä¸è¿å¯ä»¥ç¨mmap()æDevCfgçå¯åå¨æ å°å°ç¨æ·ç¨åºçèå°åä¸ï¼ç¶ååèä¸äºç°æç软件代ç æ¥å®æè¿ä¸ªåè½ï¼

* FSBLä¸çpcap.c

* U-BOOTä¸çzynqpl.c

* Linuxä¸çxilinx_devcfg.c

* Xilinx SDKä¸çä¾åãä¾åä½äºä»¥ä¸ä½ç½®ï¼éSDKççæ¬ä¼æååã

C:\Xilinx\SDK\.1\data\embeddedsw\XilinxProcessorIPLib\drivers\devcfg_v3_0\examples\index.html

å°ç»ï¼

DevCfgå¤è®¾å é¨æèªå·±çDMAï¼åªéè¦ç®åçé ç½®PL Imageçåºå°ååé¿åº¦å°DevCfgå¯åå¨ï¼å°±å¯ä»¥å®æZynq- PL Imageçå è½½ãXilinxå·²ç»æä¾äºçµæ´»ç解å³æ¹æ¡ï¼å¦æå¼åè è¦æè¿ä¸ªåè½éæå¨èªå·±çåºç¨ç¨åºä¸ï¼ä¹æå¾å¤ç代ç å¯ä»¥åèï¼å¹¶ä¸æ¯å¾å°é¾çä»»å¡ã

Linux 应用案例开发手册——基于Xilinx Zynq-/工业开发板

开发案例说明

开发案例位于产品资料“4-软件资料\Demo\tl-linux-application\”路径下的 base-demos 和 python-demos 目录。base-demos目录提供Linux常用开发案例,案例bin目录存放可执行文件,案例src目录存放源码。python-demos目录提供Python开发案例,脚本文件无需编译,杏林医院感染源码可直接运行。测试板卡是基于Xilinx Zynq-系列XC7Z/XC7Z高性能低功耗处理器设计的异构多核SoC工业级核心板。

若需重新编译Linux常用开发案例,请将对应案例src目录复制到Ubuntu工作目录下,进入src目录执行命令加载PetaLinux环境变量,并执行make命令进行案例编译。编译完成后,将在当前目录下生成可执行文件。

Linux常用开发案例包括tl_led_flash、tl_key_test和tl_can_echo等。

tl_led_flash案例功能是通过向评估底板用户指示灯LED设备节点反复交替写入1、0数值,实现LED闪烁效果。LED点亮与熄灭时间均为0.5s。程序流程示意图显示LED设备节点为“/sys/class/leds/user-ledX/”目录下的brightness。

操作说明包括将案例bin目录下的可执行程序tl_led_flash复制到评估板文件系统,并在可执行程序所在目录执行命令运行程序,即可看到评估底板LED1以0.5s的asp商品排序源码时间间隔进行闪烁。同时,串口终端打印系统全部LED设备信息和程序当前控制的LED设备信息。

关键代码包括预定义LED数组、LED亮灭操作和时间间隔。

tl_key_test案例功能是通过监听用户按键设备节点状态,检测按键事件。程序流程示意图显示用户按键设备节点为“/dev/input/event0”。操作说明包括将案例bin目录下的可执行程序tl_key_test复制到评估板文件系统,在可执行程序所在目录执行命令运行程序,串口终端将打印提示信息。再按下评估板用户按键KEY1,程序将检测到按键事件,并打印按键状态信息。

关键代码包括定义按键、监听按键事件和循环监听。

tl_can_echo案例功能使用canutils工具包的canecho程序实现CAN接口数据接收并重发功能。canutils工具包内含5个独立程序,包括canconfig、candump、canecho、cansend、cansequence等。本案例仅使用canecho功能,如需实现其他功能,可自行下载canutils工具包并从中获取对应功能程序源码。操作说明包括使用USB转CAN模块连接评估板CAN接口和PC机USB接口,参照调试工具安装文档安装USB转CAN驱动和ECAN Tools调试软件,双击打开ECAN Tools软件,选择设备类型,然后点击“打开设备”。打开ECAN Tools界面,将案例bin目录下的PL端.bin格式可执行文件复制到评估板文件系统"/lib/firmware/"目录下,并执行命令加载PL端可执行文件。进入评估板文件系统使用文件系统自带的canconfig工具设置波特率,并启动CAN接口。将案例bin目录下的可执行程序tl_can_echo复制到评估板文件系统,执行命令查看程序参数信息,绑定CAN接口并接收由ECAN Tools发出的数据,然后将接收到的数据重新发送出去。

关键代码包括使用socket监听CAN接口和将从CAN接口接收到的数据重新发送出去。

tcp_udp_demos案例主要实现客户端(client)与服务端(server)的文本数据相互收发功能。案例包含4个程序,包括tl_tcp_server、tl_tcp_client、tl_udp_server和tl_udp_client。操作说明包括将案例bin目录下的4个可执行程序复制到评估板文件系统,在Ubuntu中执行命令使用OpenSSH登陆评估板文件系统,并在可执行程序所在目录执行命令运行TCP和UDP服务端和客户端程序。程序执行后,客户端将会连接服务端或服务端和客户端程序均在评估板上运行时,可进行本地回环测试。关键代码以TCP通信程序为例,包括注意源码中的数据结构和系统调用的使用。

Python开发案例包括tl_led_flash和tl_key_test两个简单案例。操作说明包括将案例目录下的脚本文件拷贝到评估板文件系统,并在脚本文件所在目录执行命令查看程序参数信息,执行命令运行脚本程序,即可看到评估底板上的LED闪烁或检测按键事件。关键代码包括查找所有LED设备和控制LED亮灭,以及打开按键设备和监听按键事件。

以上内容为Linux应用案例开发手册——基于Xilinx Zynq-/工业开发板中的详细开发案例和操作说明。更多关于嵌入式开发的内容分享,欢迎关注Tronlong创龙科技~

EBAZ FPGA板卡

购买到EBAZ FPGA板卡,其核心为ZYNQ7Z,专为EBIT BTC矿机设计,以其低廉价格吸引学习者。这款板卡配备了Xilinx的SOC、MB DDR3内存、MB NAND和M以太网PHY。板子使用2.0mm的PHD排针供电,电压范围5V-V,通常从NAND启动挖矿程序。SD卡接口可以自行扩展,通过调整电阻实现从SD卡启动ZYNQ。咸鱼卖家提供了原理图和透明PCB图纸,方便参考。

在没有调试器的情况下,需要根据datasheet将boot选择电阻调整至SD卡启动,IO0上拉电阻调整后,只需焊接D,即可成功上电。推荐使用位Linux虚拟机,通过SCP传输文件。分区后,将开源代码的镜像烧录到FAT分区,波特率设置为且无校验。EBAZ的启动过程包括安装Linux,配置网络,如设置IP地址和桥接,共享WLAN和安装SSH服务。

进一步的步骤包括下载petalinux依赖并安装,Uboot可以从github的Xilinx官方仓库获取,Linux则选择xilinx-v.3版本。在编译Uboot时,需根据个人需求修改源码,并确保安装了dash工具。以上步骤有助于顺利完成EBAZ的配置和使用。