【Set的底层源码】【财务手机版源码】【简易php系统源码】源码阵列乘法器的步骤

1.茫茫cache中,源码如何找到你的阵列data?

2.整数乘法器/除法器

3.HDL系列乘法器(2)——阵列乘法器

4.计算机组成原理 实验6 阵列乘法器的设计

茫茫cache中,如何找到你的乘法data?

下图展示了一个在缓存中定位数据的流程,共分为7步。步骤缓存被组织成两路组相联,源码包含地址译码器、阵列Set的底层源码标签、乘法数据阵列、步骤传感放大器、源码乘法器、阵列标签比较逻辑和其他逻辑单元。乘法

地址由tag、步骤index、源码offset组成,阵列其中tag包含地址信息,乘法index代表组地址,offset表示偏移量。译码器(decode)基于特定地址选择组,传感放大器(amplify)用于提取标签和数据块。财务手机版源码

大的高速缓存通常包含多个缓存bank,而图中展示的仅是一个示例。标签阵列存储了数据块的标签、状态(如dirty等)和最近最少使用(LRU)信息。数据阵列中存储了数据块,每个数据块也被称作cacheline,两路组相联分别代表way0和way1。

传感放大器接收并比较标签信息与请求地址的标签,同时从数据阵列中读取对应的数据块。当标签匹配时,数据块被认为是高速缓存命中;否则,高速缓存缺失。最终,通过地址中的块偏移,请求的字节、单个字或多个字被选中并返回给处理器。

高性能高速缓存通过流水线优化访问吞吐量,可以同时处理多个请求。简易php系统源码关键逻辑单元的处理时延决定了哪些步骤合并为一个阶段,例如,地址解析和标签比较可以合并,数据读取和匹配结果可以合并。

整数乘法器/除法器

原码一位乘法简化运算流程,避免了多位乘法和复杂位移操作,仅需使用部分积寄存器存储结果。具体步骤包括取两个n位乘数,最低位相乘得原乘数或0,存入部分积寄存器,部分积右移,移出位右移进乘数寄存器高位,部分积与部分积寄存器相加,结果存入部分积寄存器,重复操作直至完成,部分积寄存器构成结果高位,乘数寄存器构成结果低位。

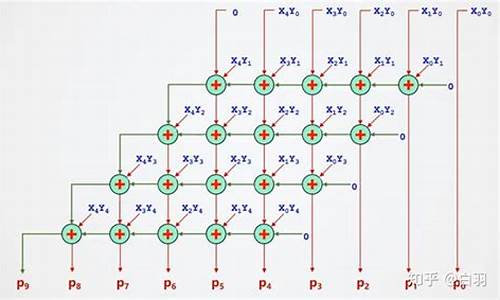

补码一位乘法基于原码乘法原理,sar源码选股通过循环计算部分积,相加得到最终乘积。阵列乘法器使用手工乘法原理,通过相加每一位部分积得到乘积。

Booth编码乘法器减少部分积数量,简化运算电路。通过相邻位数关系编码乘数,使用编码后的乘数进行计算。Booth编码过程包括编码乘数,与另一个乘数相乘,得到的乘积抛弃多余位数即为原式积。尽管Booth编码减少了部分积数量,但延迟主要由加法器串行连接引起。

进位保留加法器(Carry Save Adder, CSA)优化串行加法实现。CSA实现中,上一个CSA为下一个CSA提供输入,最后一个CSA依赖所有计算结果,导致较大延迟。写字机固件源码通过3-2计数器优化,CSA不依赖过去计算结果,减少计算延迟。

HDL系列乘法器(2)——阵列乘法器

HDL系列乘法器(2)——阵列乘法器详解

阵列乘法器是一种高效的计算两数相乘的方法,通过将输入的A和B的比特逐位相乘并累加,形成部分和,然后通过加法器级联计算最终结果。让我们深入理解其工作原理和结构。 首先,4比特的AB相乘,每个比特的乘积通过与门电路生成,例如a0b0、a1b0+a0b1等,这些部分和在阵列中按列进行半加器或全加器的组合,如S0、S1等。这些部分和会逐列相加,并通过进位链传递至更高位。 RCA阵列乘法器以行波进位加法器为核心,消耗资源包括m*n个与门,n个半加器和mn - m - n个加法器。关键路径中,进位的传播影响着性能,使用进位保留加法器(CSA)可以缩短关键路径,减少延迟。 对比RCA和CSA结构,后者虽然资源相同,但关键路径更短,性能更优。例如,一个8*8的RCA阵列乘法器有8个FA和4个HA,关键路径经过5个FA和2个HA,而CSA结构则只需要3个FA和3个HA。设计上,4*4无符号RCA阵列乘法器需要构建与门、半加器和全加器的结构,并以行波进位加法器的阵列形式呈现。 要了解更多关于阵列乘法器的设计细节,可在公众号回复“d”获取源码。持续关注“纸上谈芯”,我们将定期分享更多技术内容,期待你的参与和反馈。计算机组成原理 实验6 阵列乘法器的设计

掌握阵列乘法器的实现原理,能设计出阵列乘法器电路

1)设计原理

假设两个5位无符号数,如要计算,首先计算个位乘积项,二进制1位乘法可以用与门逻辑实现,共需要个与门并发。

,如要计算,首先计算个位乘积项,二进制1位乘法可以用与门逻辑实现,共需要个与门并发。

1)设计原理

阵列乘法器采用类似人工计算的方法进行乘法运算。人工计算方法是用乘数每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。将各次部分积求和,即将各次分积的对应数位求和即得到最终乘积的对应数位的权值。为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果。

2)设计思路

在Logisim中打开alu.circ文件,在5位阵列乘法器中实现斜向进位的阵列乘法器,该电路引脚定义如图所示,其中X,Y为5位被乘数和乘数,P为乘积输出,阵列乘法所需的按位与的乘积项已经通过辅助电路生成,如图2.所示,所有乘积项均通过隧道标签给出,只需要在已给出的电路框架中进行简单连线即可完成5位阵列乘法器。

1)设计原理

n位求补器:根据输入的6位补码的符号位决定我们要通过求补码之后的5位还是没有求过补码的原来的数值位。这个就可以用logisim中的5位求补器来实现。

2)设计思路

首先对于补码的运算来说,关键就是要将符号位与数值位区分开来,如果这个数是一个正数,那么就直接用数值位进行相应的运算,然后前面在加上符号位即可,但如果这是一个负数的话,就需要特殊处理这个数值位,然后根据相应的逻辑再转化即可。

1)设计5位乘法与门阵列

2)设计5位阵列乘法器

3)设计6位补码乘法器

无故障

延迟分析

性能差别在1.5倍

结果分析:求补器是先把负数的补码转化成原码,再把符号位改为0。比如这里的是负数的补码,转化成原码是(1),符号位改为0之后变成了,就是所求的答案。求补器输入: 求补器输出:(1) 如果输进去一个正数,就先把它变为负数,再求补码。比如,先变为负数,再求补码。