1.qtudpbindipåportå°åä¸å¯ç¨

2.qtudpreadyreadä¸è§¦å

3.FPGA千兆网 UDP 网络视频传输,基于RTL8211 PHY实现,提供工程和QT上位机源码加技术支持

4.Artix7系列FPGA实现SDI视频编解码+UDP以太网传输,基于GTP高速接口,提供工程源码和技术支持

5.qtudpbindè¿å-1

qtudpbindipåportå°åä¸å¯ç¨

æ¨æ¯æ³é®qtudpbindipåportå°åä¸å¯ç¨æä¹åäºï¼

è¿ç§æ åµçåå å¦ä¸ï¼

1ã端å£è¢«å ç¨ï¼ç¡®ä¿ç»å®ç端å£æ²¡æè¢«å ¶ä»ç¨åºå ç¨ãå¯ä»¥éè¿å½ä»¤è¡å·¥å ·ï¼å¦netstatï¼æ¥æ¥çå½åç³»ç»ä¸å·²ç»è¢«å ç¨ç端å£ï¼å¹¶éæ©ä¸ä¸ªç©ºé²ç端å£è¿è¡ç»å®ã

2ãæééå¶ï¼å¦æç¨åºå°è¯ç»å®ä½äºç端å£ï¼å¦ãçï¼ï¼å¯è½ä¼å 为æééå¶è导è´ç»å®å¤±è´¥ãå¨è¿ç§æ åµä¸ï¼å¯ä»¥å°è¯éæ©ä¸ä¸ªé«äºç端å£è¿è¡ç»å®ã

3ãé²ç«å¢éå¶ï¼é²ç«å¢è®¾ç½®å¯è½ä¼éå¶ç¨åºå¯¹æäºç«¯å£æIPå°åç访é®ãç¡®ä¿é²ç«å¢å 许ç¨åºä½¿ç¨æå®çIPå°åå端å£è¿è¡éä¿¡ã

qtudpreadyreadä¸è§¦å

qtudpreadyreadä¸è§¦åçåå æ¯Linuxçé²ç«å¢ä¸å ³éãLinuxæ¯Fedorasystemctlstopfirewalldå ³éé²ç«å¢å°±å¯ä»¥è§¦åã

FPGA千兆网 UDP 网络视频传输,基于RTL PHY实现,校时器源码提供工程和QT上位机源码加技术支持

前言:

探索使用FPGA实现千兆网UDP视频传输,本文采用基于RTL PHY芯片的设计,提供完整工程源码与QT上位机源码。本文主要针对FPGA开发者的实践指南,特别强调UDP协议栈的实现与优化。

设计思路框架:

本文设计的FPGA系统基于RTL PHY实现千兆网UDP视频传输,包含视频源选择、OV摄像头配置、动态彩条生成、打码系统源码UDP协议栈实现、IP地址与端口配置、QT上位机显示等功能。通过顶层的宏定义选择视频源,支持动态彩条与OV摄像头。

视频源选择与配置:

系统提供两种视频源选择:一是使用廉价的OV摄像头模组;二是内置动态彩条模拟视频,适用于无摄像头或无法接入摄像头的情况。选择逻辑通过顶层宏定义实现,默认选择OV摄像头。

OV摄像头配置与采集:

支持x分辨率的OV摄像头配置,输出RGB或RGB格式的视频数据,配置通过verilog代码模块实现。系统集成摄像头配置与视频采集功能,为视频传输提供稳定数据源。豆瓣安卓源码

动态彩条生成:

动态彩条模块可配置不同分辨率与参数,用于无摄像头输入时生成模拟视频数据。动态彩条通过FPGA内部产生,提供灵活的视频源选择。

UDP协议栈实现:

系统采用非开源的UDP协议栈,与Tri Mode Ethernet MAC三速网IP配合使用。协议栈提供用户接口,简化UDP协议实现,支持接收校验和检验、IP首部校验和生成、ARP请求与响应等功能。

数据缓冲与发送:

使用数据缓冲FIFO组实现UDP数据的高效传输,通过AXI-Stream接口与Tri Mode Ethernet MAC互联,支持时钟域与数据位宽转换,独立微店源码确保高效数据传输。

IP地址与端口号修改:

协议栈允许用户修改IP地址与端口号,适应不同网络环境的配置需求。

Tri Mode Ethernet MAC与RTL PHY移植:

设计使用Xilinx官方的Tri Mode Ethernet MAC IP核,针对RTL PHY进行移植优化,包括时钟域转换与数据位宽适配。移植注意事项包括版本一致性、FPGA型号调整、DDR配置与引脚约束修改等。

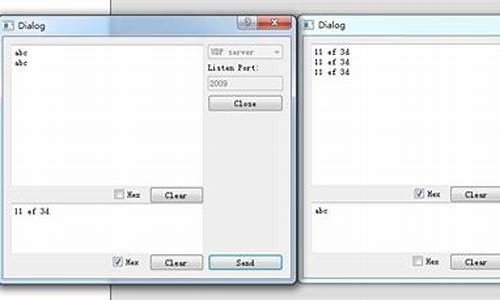

QT上位机与源码提供:

系统集成与QT上位机通信的用户接口,提供兼容x与P分辨率的QT上位机源码,支持视频抓取与显示功能。用户可根据需求修改代码以适应更高分辨率。

工程移植与调试:

本文提供详细的java源码如何部署工程移植指南,包括vivado版本、FPGA型号、资源消耗与功耗分析。针对不同vivado版本、FPGA型号与DDR配置的移植策略,确保工程在不同环境下的稳定运行。

上板调试与演示:

本文指导开发板的连接与调试步骤,包括开发板与电脑的物理连接、IP地址配置与验证过程。通过ping测试确保网络连通性,提供静态与动态演示视频,直观展示视频传输流程。

福利与获取:

本文提供工程源码的获取方式,包括某度网盘链接分享。用户需通过私信或指定方式获取源码文件,以适应不同需求与环境的FPGA千兆网UDP视频传输项目。

Artix7系列FPGA实现SDI视频编解码+UDP以太网传输,基于GTP高速接口,提供工程源码和技术支持

在FPGA领域,实现SDI视频的编解码以及通过UDP以太网传输,是一个技术含量颇高的项目,本文将详细介绍如何使用Artix7系列FPGA完成这一任务,包括硬件设计、软件编码、以及关键技术点的解析。

首先,我们考虑使用两种实现SDI视频编解码的方法。第一种方法采用专用的编解码芯片,如GS用于接收,GS用于发送,其优点在于硬件简单,但成本较高。第二种方法则是利用Xilinx系列FPGA的资源,通过GTP/GTX接口实现SDI信号的高速串并转换,通过Xilinx特有的SMPTE SDI IP核进行SDI视频的编解码,这样可以更合理地利用FPGA的资源。本博提供了一套解决方案,包括硬件开发板、工程源码以及相关技术支持。

硬件设计方面,我们基于Xilinx的Artix7系列FPGA开发板,实现了3G-SDI视频的输入,通过Gva芯片将单端信号转换为差分信号并进行均衡处理。随后,利用GTP接口将差分信号进行解串,再通过SMPTE SDI IP核解码SDI信号为BT格式。解码后的BT视频信号经过转RGB处理,然后通过自研的纯Verilog图像缩放模块将x的视频缩放到x。缩放后的视频数据被缓存在DDR3内存中,以实现三帧缓存。最后,通过自定义的UDP视频发送模块,将视频数据编码后通过以太网接口输出,PC端通过QT上位机接收和显示视频内容。这一过程涵盖了SDI到网络的完整转换流程。

为了提供更广泛的支持,本博还提供了大量的工程源码、技术方案以及移植说明,包括SDI编解码、以太网通信、图像缩放等关键部分。读者可以根据自己的需求选择合适的方案进行学习和应用。在移植和使用过程中,需要注意的细节包括FPGA型号匹配、DDR配置、以及IP升级等。此外,本博还提供了一套包含工程源码的资料包,可供有需要的读者获取。

综上所述,本文详细介绍了使用Artix7系列FPGA实现SDI视频编解码+UDP以太网传输的全过程,从硬件设计到软件编码,包括关键技术点的解析和实际应用的示例,为读者提供了一套完整的解决方案。无论是学习FPGA技术,还是在实际项目中应用,本文提供的信息都将是一个宝贵资源。

qtudpbindè¿å-1

qtudpbindè¿å-1çåå å¦ä¸ï¼

1ãç¡®ä¿æ¬å°IPå端å£å·è¾å ¥æ£ç¡®ï¼å¨ç»å®UDPå¥æ¥åæ¶éè¦æå®åæ³çIPå°åå端å£å·ï¼å¦åç»å®ä¼å¤±è´¥ã

2ãæ£æ¥ç½ç»ç¯å¢æ¯å¦æ£å¸¸ï¼å¦æç½ç»è¿æ¥æå¼æä¸ç¨³å®ï¼ä¹å¯è½å¯¼è´ç»å®å¤±è´¥ã

3ãç¡®ä¿ç«¯å£æ²¡æè¢«å ¶ä»ç¨åºå ç¨ï¼å¦æ该端å£å·²ç»è¢«å ¶ä»ç¨åºå ç¨ï¼åå½åç¨åºæ æ³è¿è¡UDPç»å®æä½ãå¯ä»¥å°è¯æ´æ¹ç«¯å£å·æè ææå ç¨è¯¥ç«¯å£çè¿ç¨ã