【wml源码提取】【dubbo源码解剖】【atomic源码分析】ddr源码

1.ddrԴ??

2.一直有个疑问,为什么windows设备管理器里面没有“内存”这

3.Ebaz4205 Zynq7010 memcpy性能

4.sdr开发篇 6. zynq+ad9361的linux工程搭建

5.FPGA使用MIG调用SODIMM内存条接口教程,提供vivado工程源码和技术支持

ddrԴ??

本篇内容不讲解uboot源码,只总结面试中高频问到的重要知识点。内容适用于嵌入式新人了解uboot,对老手有复习和查漏补缺的作用。

1、wml源码提取PC机启动:上电后,BIOS程序初始化DDR内存和硬盘,从硬盘读取OS镜像到DDR,跳转执行OS。

2、嵌入式Linux系统启动:上电后执行uboot,初始化DDR、Flash,将OS从Flash读到DDR,启动OS。

3、uboot定义与作用:uboot属于bootloader,作为单线程裸机程序,主要作用是初始化硬件、内存、flash等,引导内核启动。dubbo源码解剖

4、uboot启动阶段(不同平台差异):MTK平台:boot rom -> preloader -> lk -> kernel;RK平台:bootrom -> spl(miniloader) -> uboot -> trust -> kernel;NXP平台:bootrom -> bl2 -> ATF -> uboot -> kernel。

5、uboot支持多种启动方式:SPI Flash/eMMC/Nvme/SD/Hard Disk/U-Disk/net。启动方式不同,固件存放位置也不同。

6、掌握uboot的关键点:命令和环境变量。uboot启动后大部分工作在shell中完成,命令用于操作,环境变量如bootcmd和bootargs,用于设置启动参数。

7、bootargs参数详解:root用于指定rootfs位置,console用于设置控制台,mem用于指定内核使用内存大小,ramdisk_size用于设置ramdisk大小,initrd用于指定initrd参数,init用于指定启动脚本,mtdparts用于设置分区。

8、常用bootargs组合:文件系统为ramdisk、atomic源码分析jffs2类型、nfs等不同情况下的bootargs设置示例。

总结,了解uboot是嵌入式开发的基础,掌握其启动过程和关键参数,对提高开发效率和解决问题有重要作用。

一直有个疑问,为什么windows设备管理器里面没有“内存”这

内存的初始化在BIOS或UEFI过程中进行,这决定了是否能启动Windows操作系统。若内存识别出现问题,系统无法启动,也不会显示任何视频输出,这被称为“点不亮”现象。

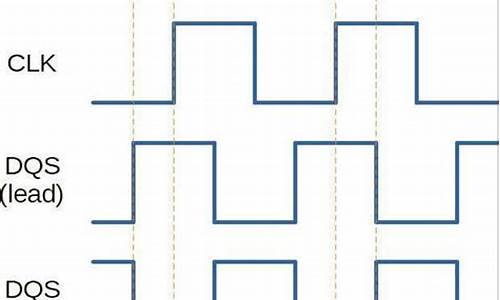

在这一过程中,内存驱动实际上作为固件的一部分出现,如Intel的FSP或AMD的AGESA,通常是封闭源代码的软件。其主要工作是“memory train”,即按照设置探测和设置DDR内存的时序。

一些ARM处理器支持DDR内存的动态电压调整,因此Linux中存在内存控制器的驱动,如RK的内存控制器驱动。而Windows似乎不支持DDR内存的源码打包分享动态电压调整,因此没有专门的内存控制器驱动。

初始化内存的功能由固件完成,而一些内存控制器的功能则由驱动程序执行,通常作为芯片组驱动的一部分安装在系统中。例如,在Windows上,WHEA可以报告ECC内存错误,而名为PSHED的插件驱动则提供额外的错误报告,专用于特定平台的硬件错误驱动程序插件。

内存控制器还包含性能计数器(PMU),Intel VTune等工具可以使用驱动扩展访问这些性能数据。

Ebaz Zynq memcpy性能

eba 板卡在Linux环境下的DDR测试结果显示,在SDK源码环境NonOS中进行ZYNQ pdk自带的memcpy性能测试。

针对ZYNQ测量时间代码,通过获取全局定时器的时间值,基准为系统主频二分频。

定义COUNTS_PER_SECOND,表示每秒计数值(基于CPU频率除以2)。

在测试中添加内存拷贝代码,使用MB大小进行操作。

经过计算,得出memcpy的go rpc源码运行速度。

通过反汇编ELF代码,可以进一步分析和理解memcpy的具体执行过程和性能表现。

sdr开发篇 6. zynq+ad的linux工程搭建

SDR开发过程中,我们首先从hdl源码开始,从github下载_r1分支的zip包,解压后放置在工作区~/work/zynq_dev/ados。然后,创建Vivado工程,配置环境并编译,需要注意的是,这个工程需要针对xmzed进行修改。接着,对DDR和EMIO接口进行适配,并导出HDF文件。

接着,我们进入Petalinux 2.1工程阶段,拷贝适配后的HDF文件,并从github获取ADI的Linux内核和meta-adi。内核和meta-adi需下载、解压并配置,硬件信息目录中需要设置唯一的HDF文件。初次配置后,后续只需在修改后重新编译,配置启动方式、接口、SD卡,并解决source bitbake失败的问题。

内核配置中,USB和IIO功能默认开启。设备树部分,需在dash环境下修改,并在device-tree.bbappend中添加自定义设置。root文件系统配置时,由于meta-adi的影响,需要调整petalinux-user-image.bbappend以恢复默认设置。

编译工程时,注意分配足够的CPU资源,可能需要解决网络问题并设置全局代理。遇到错误时,如jesd-status-dev-r0的fetch问题,需替换相关文件。最后,打包boot.bin并制作SD卡文件系统,包括EXT和FAT分区,并进行启动测试。

测试阶段,通过拨码开关启动设备,使用默认root/root登录,进行IIO连接测试和Gnuradio发送信号测试。整个过程参考了相关教程和文档,如AD的开发指南和Linux驱动等。

FPGA使用MIG调用SODIMM内存条接口教程,提供vivado工程源码和技术支持

在FPGA应用中,数据缓存扮演着至关重要的角色,尤其在图像处理、AD采集及PCIe等领域。通常,FPGA会配备SDRAM、DDR3或DDR4等内存颗粒作为缓存资源,但有时受限于I/O端口或FPGA型号,可能需要额外设计SODIMM适配器以满足更高数据缓存需求。本文将介绍使用Xilinx V7 FPGA开发板NetFPGA-SUME平台实现SODIMM内存条接口的详细教程,并提供完整的vivado工程源码和技术支持,适用于学生、研究项目及在职工程师的学习与实践。

实验板载有2个SODIMM接口,可插入内存条作为缓存,支持在FPGA开发板上进行视频缓存、处理和显示的测试。本例程使用HDMI输入视频或内部生成的彩条视频作为数据源,将视频缓存到SODIMM内存条中,进行三帧缓存后再输出至HDMI端口显示。成功或失败可通过输出图像质量直观判断,进而验证FPGA与SODIMM内存条的读写功能。

本文提供了完整的工程源码和使用指南,旨在帮助读者快速掌握FPGA使用SODIMM内存条接口的实现方法,并支持项目移植。内容涵盖从设计思路、硬件接口、内存配置到VGA时序生成的详细步骤,适用于医疗、军工等高速接口或图像处理领域的专业应用。

请阅读至文章末尾以获取完整工程源码和技术支持的获取方式。请注意,本工程源码的使用仅限于个人学习和研究,禁止用于商业目的。若在使用过程中遇到问题或有建议,欢迎通过私信进行交流。

为了确保本教程的实用性与合法性,部分源码和资源可能通过网络渠道获取,包括CSDN、Xilinx官网、Altera官网等。若在使用过程中发现任何侵权行为,请私信博主予以纠正。本教程及其相关资源仅供个人学习使用,博主不承担任何因个人使用导致的法律责任。

在设计过程中,首先介绍了SODIMM内存条的基本信息及特点,与现代主板相比,它在紧凑性和灵活性上具有一定优势。接下来,设计思路包括了视频输入、缓存、SODIMM内存条配置、VGA时序生成及视频输出等关键步骤。

视频输入部分,利用FMC接口接入HDMI输入或动态彩条视频源,其中HDMI输入通过silcom芯片解码,动态彩条视频则作为模拟输入源。视频缓存采用FDMA控制器实现,适用于各种类型数据的读写操作。MIG配置调用SODIMM内存条的关键在于正确配置内存参数以适应特定的内存条类型。

VGA时序驱动的实现确保了视频流的正确输出,通过Verilog源码提供支持,可灵活调整分辨率。最后,视频输出通过HDMI接口实现,利用silcom芯片进行编码,完成从FPGA到显示设备的视频传输。

本教程详细解析了从硬件配置到软件实现的全过程,包括Vivado工程的设置、综合编译结果分析及上板调试验证。通过实际案例,展示了如何在FPGA开发板上利用SODIMM内存条进行数据缓存和处理。

为了确保读者能够轻松获取到工程源码,提供了链接方式获取完整资源,确保学习者能够直接实践和应用教程内容。请注意遵守资源获取的规则,仅用于个人学习与研究目的。