1.EDA课ç¨è®¾è®¡ï¼ç¨VHDLç¼ç¨ååºç§è½¦è®¡è´¹å¨

2.欧陆590功能特点

3.车牌识别项目(CCPD数据集)

4.江西便宜直流调速器诚信服务

5.江苏欧陆直流调速器性价比价格

EDA课ç¨è®¾è®¡ï¼ç¨VHDLç¼ç¨ååºç§è½¦è®¡è´¹å¨

课ç¨è®¾è®¡å 容ä¸è¦æ±

1ï¼ç¨å¼å ³æé®è¡¨ç¤ºèå²ï¼æ¯ä¸ªèå²ä»£è¡¨ç±³ï¼ä¸ªèå²1å ¬éï¼æ¯å ¬é1.4å ï¼è½åæ¥æ¾ç¤ºéç¨åè´¹ç¨ï¼

2ï¼ä½äº2å ¬é5å 计费ï¼é«äº2å ¬éæ»è´¹ç¨=èµ·æ¥è´¹ç¨+ï¼éç¨-2å ¬éï¼*éç¨åä»·+

çåæ¶é´*çååä»·ï¼

3ï¼çåæ¶é´å¤§äº2åéï¼ææ¯åé1.3å 计费ï¼

4ï¼å¯ä»¥è®¾å®èµ·æ¥ä»·åéç¨åä»·ã

ä¸ã设计åçä¸ææ¯æ¹æ³ï¼

å æ¬ï¼çµè·¯å·¥ä½åçåæä¸åçå¾ãå å¨ä»¶éæ©ä¸åæ°è®¡ç®ãçµè·¯è°è¯æ¹æ³ä¸ç»æ说æï¼

软件设计说æ书ä¸æµç¨å¾ã软件æºç¨åºä»£ç ã软件è°è¯æ¹æ³ä¸è¿è¡ç»æ说æã

æ ¹æ®è®¾è®¡è¦æ±ï¼ç³»ç»çè¾å ¥ä¿¡å·clkï¼è®¡ä»·å¼å§ä¿¡å·startï¼çå¾ ä¿¡å·stopï¼éç¨èå²ä¿¡å·finãç³»ç»çè¾åºä¿¡å·æï¼æ»è´¹ç¨æ°C0âc3ï¼è¡é©¶è·ç¦»k0âk1ï¼çå¾ æ¶é´m0âm1çãç³»ç»æ两个èå²è¾å ¥ä¿¡å·clk_k,速停p使fin,å ¶ä¸clk_kå°æ ¹æ®è®¾è®¡è¦æ±åé¢æhzï¼hzå1hzåå«ä½ä¸ºå ¬é计费åè¶ æ¶è®¡è´¹çèå²ã两个æ§å¶è¾å ¥å¼å ³startï¼stopï¼æ§å¶è¿ç¨ä¸ºï¼startä½ä¸ºè®¡è´¹å¼å§çå¼å ³ï¼å½start为é«çµå¹³æ¶ï¼ç³»ç»å¼å§æ ¹æ®è¾å ¥çæ åµè®¡è´¹ãå½æä¹å®¢ä¸è½¦å¹¶å¼å§è¡é©¶æ¶ï¼finèå²å°æ¥ï¼è¿è¡è¡é©¶è®¡è´¹ï¼æ¤æ¶çstopéè¦ç½®ä¸º0ï¼å¦éå车çå¾ ï¼å°±æstopå为é«çµå¹³ï¼

并å»é¤finè¾å ¥èå²ï¼è¿è¡çå¾ è®¡è´¹ï¼å½ä¹å®¢ä¸è½¦ä¸ä¸çå¾ æ¶ï¼ç´æ¥å°start置为0ï¼ç³»ç»åæ¢å·¥ä½ï¼ä»·æ ¼å¼å§å½ä¸ºèµ·æ¥ä»·5.0å ã

æ´ä¸ªè®¾è®¡ç±åé¢æ¨¡åï¼è®¡é模åï¼è®¡è´¹æ¨¡åï¼æ§å¶æ¨¡ååæ¾ç¤ºæ¨¡åäºä¸ªé¨åç»æã

å ¶ä¸è®¡é模åæ¯æ´ä¸ªç³»ç»å®ç°éç¨è®¡æ°åæ¶é´è®¡æ°çéè¦é¨åï¼æ§å¶æ¨¡åæ¯å®ç°ä¸å计费æ¹å¼çéæ©é¨åï¼æ ¹æ®æ设计ç使è½ç«¯éæ©æ¯æ ¹æ®éç¨è®¡è´¹è¿æ¯æ ¹æ®çå¾ æ¶é´è®¡è´¹ï¼åæ¶è®¾è®¡éè¿åé¢æ¨¡å产çä¸åé¢ççèå²ä¿¡å·æ¥å®ç°ç³»ç»ç计费ã计é模åéç¨1hzç驱å¨ä¿¡å·ï¼è®¡è´¹æ¨¡åéç¨hzï¼hzç驱å¨ä¿¡å·ï¼è®¡é模åæ¯è®¡æ°ä¸æ¬¡ï¼è®¡é模åå°±å®ç°æ¬¡æè 次计æ°ï¼å³ä¸ºå®ç°è®¡æ¶ç1.3å /minï¼è®¡ç¨æ¶ç1.4å /kmçæ¶è´¹ãç»ææ¡å¾å¦ä¸æ示ï¼

1.ç¾è¿å¶æ¨¡åï¼

å®ç°ç¾ç±³èå²ç驱å¨ä¿¡å·ï¼å 件æ¡å¾å¦å¾3æ示ï¼

å¾3 ç¾è¿å¶æ¨¡åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

entity baijinzhi is

port(start,clk2: in std_logic; --ç§èå²

a: out std_logic_vector(3 downto 0));

end baijinzhi;

architecture rt1 of baijinzhi is

signal count_1:std_logic_vector(3 downto 0);

begin

a<=count_1;

process(start,clk2)

begin

if(start='0')then

count_1<="";

elsif(clk2'event and clk2='1')then

if(count_1="")then

count_1<="";

else

count_1<=count_1+'1';

end if;

end if;

end process;

end rt1

2.计费模å

; å®ç°éç¨åçåæ¶é´ç计费并è¾åºå°æ¾ç¤ºï¼å 件æ¡å¾4å¦ä¸ï¼

å¾4 计费模åæ¡å¾

æºç¨åºå¦ä¸ï¼

Library IEEE;

use IEEE.std_logic_.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity jifei is

port(clk2:in std_logic; --计费驱å¨ä¿¡å·

start:in std_logic; --计费å¼å§ä¿¡å·

c0,c1,c2,c3:buffer std_logic_vector(3 downto 0));

end jifei;

architecture rt1 of jifei is

begin

process(clk2,start)

begin

if start='0'then c3<="";c2<="";c1<="";c0<=""; --èµ·æ¥ä»·5å

elsif clk2'event and clk2='1'then

if c0="" then c0<="";

if c1="" then c1<="";

if c2="" then c2<="";

if c3="" then c3<="";

else c3<=c3+1;

end if;

else c2<=c2+1;

end if;

else c1<=c1+1;

end if;

else c0<=c0+1;

end if;

end if;

end process;

end rt1;

3.å ¬é模å

å®ç°åç¨ç计æ°åè¾åºè®¡è´¹èå²ï¼å 件æ¡å¾5å¦ä¸ï¼

å¾5 å ¬é模åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

entity gongli is

port(clk1,start: in std_logic; --ç¾ç±³èå²

k1,k2,k3,k4: out std_logic_vector(3 downto 0); --éç¨æ¾ç¤º

temp2 : out std_logic);

end gongli;

architecture rt1 of gongli is

signal count_1: std_logic_vector(3 downto 0);

signal count_2: std_logic_vector(3 downto 0);

signal count_3: std_logic_vector(3 downto 0);

signal count_4: std_logic_vector(3 downto 0);

begin

k1<=count_1;

k2<=count_2;

k3<=count_3;

k4<=count_4;

process(start,clk1)

begin

if(start='0')then

count_1<="";

count_2<="";

count_3<="";

count_4<=""; ---å ¬éæ¸ é¶

elsif(clk1'event and clk1='1')then

if(count_1="")then --å ¬é计æ°å¨

count_1<="";count_2<=count_2+1;temp2<='1';

if(count_2="")then

count_2<="";count_3<=count_3+'1';

if(count_3="")then

count_3<="";count_4<=count_4+'1';

end if;

end if;

else

count_1<=count_1+'1';temp2<='0';

end if;

end if;

end process;

end rt1;

4.è¾åºæ¨¡å

å®ç°æææ°æ®çè¾åºï¼å 件æ¡å¾6å¦ä¸ï¼

å¾6 è¾åºæ¨¡åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

entity shuchu is

port(y: in std_logic_vector(3 downto 0);

e: out std_logic_vector(6 downto 0));

end shuchu;

architecture rt1of shuchu is

begin

process

begin

case y is

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when""=>e<="";

when others=>e<="";

end case;

end process;

end rt1;

5.æ¾ç¤ºæ¨¡å

å®ç°æææ°æ®çæ¾ç¤ºï¼å 件æ¡å¾7å¦ä¸ï¼

å¾7 æ¾ç¤ºæ¨¡åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

entity xianshi is

port(start: in std_logic;

a:in std_logic_vector(3 downto 0); --éæ©ä¿¡å·

c1,c2,c3,c4,out1,out2,out3,out4:in std_logic_vector(3 downto 0); --éç¨æ¾ç¤º,æ¶é´æ¾ç¤ºè¾å ¥

y:out std_logic_vector(3 downto 0)); --éç¨æ¾ç¤º,æ¶é´æ¾ç¤ºè¾åº

end xianshi;

architecture rt1 of xianshi is

begin

process

begin

if(start='0')then

y<="";

else case a is

when ""=> y<=c1 ;

when ""=> y<=c2 ;

when ""=> y<=c3 ;

when ""=> y<=c4 ;

when ""=> y<=out1 ;

when ""=> y<=out2;

when ""=> y<=out3 ;

when ""=> y<=out4;

when others =>y<= "";

end case;

end if;

end process;

end rt1;

6.dian模å

å¾8 dian模åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

entity dian is

port(a: in std_logic_vector(3 downto 0);

e: out std_logic);

end dian;

architecture rt1 of dian is

begin

process

begin

case a is

when ""=>e<='1';

when ""=>e<='1';

when others=>e<='0';

end case;

end process;

end rt1;

ä¸ãä¸å个模å设计åæ

ç³»ç»æ»ä½é¡¶å±æ¡å¾å¦ä¸ï¼

ç³»ç»æ»ä½é¡¶å±æ¡å¾

ç¨åºæç»åè½å®ç°æ³¢å½¢ä»¿ç

1. åé¢æ¨¡å

ç±äºå®éªç®±ä¸æ²¡æhzåhzçæ´æ°åæ¶éä¿¡å·ï¼å æ¤éç¨é¢çè¾å¤§çkhzè¿è¡åé¢ï¼ä»¥è¿ä¼¼å¾å°hzï¼hzå1hzçæ¶éé¢çãéè¿ä»¥ä¸ä¸ç§ä¸åé¢ççèå²ä¿¡å·å®è¡åºç§è½¦è¡é©¶ï¼çå¾ ä¸¤ç§æ åµä¸çä¸å计费ã模åå 件å¦ä¸ï¼

åé¢æ¨¡åæ¡å¾

æºç¨åºå¦ä¸ï¼

Library IEEE;

use IEEE.std_logic_.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity fenpin is

port(clk_k:in std_logic; --ç³»ç»æ¶é

clk_:buffer std_logic; --åé¢

clk_:buffer std_logic; --åé¢

clk_1 : buffer std_logic); --1åé¢

end fenpin ;

architecture rt1 of fenpin is

signal q_:integer range 0 to ; --å®ä¹ä¸é´ä¿¡å·é

signal q_:integer range 0 to ;

signal q_1:integer range 0 to ;

begin

process(clk_k)

begin

If(clk_k' event and clk_k='1')then

If q_= then q_<=0;clk_<=not clk_;

else q_<=q_+1;

end if; --å¾hzé¢çä¿¡å·

If q_= then q_<=0;clk_<=not clk_;

else q_<=q_+1;

end if; --å¾hzé¢çä¿¡å·

If q_1= then q_1<=0;clk_1<=not clk_1;

else q_1<=q_1+1;

end if; --å¾1hzé¢çä¿¡å·

end if;

end process;

end rt1ï¼

2. 计é模å

计é模å主è¦å®æ计æ¶å计ç¨åè½ã

计æ¶é¨åï¼è®¡ç®ä¹å®¢ççå¾ ç´¯ç§¯æ¶é´ï¼å½çå¾ æ¶é´å¤§äº2minæ¶ï¼æ¬æ¨¡åä¸en1使è½ä¿¡å·å为1ï¼å½clk1æ¯æ¥ä¸ä¸ªä¸å沿ï¼è®¡æ¶å¨å°±èªå¢1ï¼è®¡æ¶å¨çéç¨ä¸ºminï¼æ»¡éç¨åèªå¨å½é¶ã

计ç¨é¨åï¼è®¡ç®ä¹å®¢æè¡é©¶çå ¬éæ°ï¼å½è¡é©¶éç¨å¤§äº2kmæ¶ï¼æ¬æ¨¡åä¸en0使è½ä¿¡å·å为1ï¼å½clkæ¯æ¥ä¸ä¸ªä¸å沿ï¼è®¡ç¨å¨å°±èªå¢1ï¼è®¡ç¨å¨çéç¨ä¸ºkmï¼æ»¡éç¨åèªå¨å½é¶ã

å 件æ¡å¾ä¸ºï¼

计é模åæ¡å¾

计é模å仿ç波形为ï¼

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity jiliang is

port(start:in std_logic; --计费å¼å§ä¿¡å·

fin:in std_logic; --éç¨èå²ä¿¡å·

stop:in std_logic; --è¡é©¶ä¸éçå¾ ä¿¡å·

clk1:in std_logic; --驱å¨èå²

en1,en0:buffer std_logic; --计费å价使è½ä¿¡å·

k1,k0:buffer std_logic_vector(3 downto 0); --è¡é©¶å ¬é计æ°

m1,m0:buffer std_logic_vector(3 downto 0)); --çå¾ æ¶é´è®¡æ°

end jiliang;

architecture rt2 of jiliang is

signal w:integer range 0 to ; --计æ¶èå´0~

begin

process(clk1)

begin

if(clk1'event and clk1='1')then

if start='0' then

w<=0;en1<='0';en0<='0';m1<="";

m0<="";k1<="";k0<="";

elsif stop='1' then --计æ¶å¼å§ä¿¡å·

if w= then

w<=0;

else w<=w+1;

end if;

if m0="" then

m0<="";

if m1="" then

m1<="";

else m1<=m1+1;

end if;

else m0<=m0+1;

end if;

if stop='1' then en0<='0';

if m1&m0>"" then en1<='1'; --è¥çå¾ æ¶é´å¤§äº2minåen1ç½®1

else en1<='0';

end if;

end if;

elsif fin='1' then --éç¨è®¡æ°å¼å§

if k0="" then k0<="";

if k1="" then k1<=""; --计ç¨èå´0~

else k1<=k1+1;

end if;

else k0<=k0+1;

end if;

if stop='0' then

en1<='0';

if k1&k0>"" then

en0<='1'; --è¥è¡ä½¿éç¨å¤§äº2kmï¼åen0ç½®1

else en0<='0';

end if;

end if;

end if;

end if;

end process;

end rt2;

3. æ§å¶æ¨¡å

æ¬æ¨¡å主è¦æ¯éè¿è®¡é模å产çç两个ä¸åçè¾å ¥ä½¿è½ä¿¡å·en0ï¼en1ï¼å¯¹æ¯ä¸ªåé¢æ¨¡åè¾åºçhzï¼hzçèå²è¿è¡éæ©è¾åºçè¿ç¨ï¼æ¬æ¨¡åå®ç°äºåèå²çäºéä¸ï¼æç»ç®ç为äºè®¡è´¹æ¨¡åä¸å¯¹è¡é©¶è¿ç¨ä¸ä¸åçæ¶æ®µè¿è¡è®¡ä»·ã

模åå 件å¦ä¸ï¼

æ§å¶æ¨¡åæ¡å¾

æ§å¶æ¨¡å仿ç波形为ï¼

æºç¨åºå¦ä¸ï¼

Library IEEE;

use IEEE.std_logic_.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity kongzhi is

port(en0,en1:in std_logic; --使è½éæ©ä¿¡å·

clk_in1:in std_logic; --åé¢è¾å ¥ä¿¡å·

clk_in2:in std_logic; --åé¢è¾å ¥ä¿¡å·

clk_out:out std_logic); --è¾åºä¿¡å·

end kongzhi;

architecture rt3 of kongzhi is

begin

process(en0,en1)

begin

if en0='1' then --å®ç°äºéä¸åè½

clk_out<=clk_in1;

elsif en1='1' then

clk_out<=clk_in2;

end if;

end process;

end rt3;

4.计费模å

å½è®¡è´¹ä¿¡å·startä¸ç´å¤äºé«çµå¹³å³è®¡è´¹ç¶ææ¶ï¼æ¬æ¨¡åæ ¹æ®æ§å¶æ¨¡åéæ©åºçä¿¡å·ä»è对ä¸åçåä»·æ¶æ®µè¿è¡è®¡è´¹ãå³è¡ç¨å¨2kmå ï¼èä¸çå¾ ç´¯è®¡æ¶é´å°äº2minå为起æ¥ä»·5å ï¼2kmå¤ä»¥æ¯å ¬é1.4.å 计费ï¼çå¾ ç´¯ç§¯æ¶é´è¶ è¿2minåææ¯åé1.3å 计费ãc0ï¼c1ï¼c2ï¼c3åå«è¡¨ç¤ºè´¹ç¨çæ¾ç¤ºã

模åå 件为ï¼

计费模åæ¡å¾

计费模å仿ç波形为ï¼

æºç¨åºå¦ä¸ï¼

Library IEEE;

use IEEE.std_logic_.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity jifei is

port(clk2:in std_logic; --计费驱å¨ä¿¡å·

start:in std_logic; --计费å¼å§ä¿¡å·

c0,c1,c2,c3:buffer std_logic_vector(3 downto 0));

end jifei;

architecture rt4 of jifei is

begin

process(clk2,start)

begin

if start='0'then c3<="";c2<="";c1<="";c0<=""; --èµ·æ¥ä»·5å

elsif clk2'event and clk2='1'then

if c0="" then c0<="";

if c1="" then c1<="";

if c2="" then c2<="";

if c3="" then c3<=""; --计价èå´0~.9

else c3<=c3+1;

end if;

else c2<=c2+1;

end if;

else c1<=c1+1;

end if;

else c0<=c0+1;

end if;

end if;

end process;

end rt4;

5.æ¾ç¤ºæ¨¡å

æ¾ç¤ºæ¨¡åå®æ计价ï¼è®¡æ¶å计ç¨æ°æ®æ¾ç¤ºã计费æ°æ®éå ¥æ¾ç¤ºæ¨¡åè¿è¡è¯ç ï¼æåéè³ä»¥ç¾å ï¼åå ï¼å ï¼è§ä¸ºåä½å¯¹åºçæ°ç 管ä¸æ¾ç¤ºã计æ¶æ°æ®éå ¥æ¾ç¤ºæ¨¡åè¿è¡è¯ç ï¼æåéè³ä»¥å为åä½å¯¹åºçæ°ç 管ä¸æ¾ç¤ºã计ç¨æ°æ®éå ¥æ¾ç¤ºæ¨¡åè¿è¡è¯ç ï¼æåéè³ä»¥km为åä½çæ°ç 管ä¸æ¾ç¤ºã

模åå 件为ï¼

æ¾ç¤ºæ¨¡åæ¡å¾

æºç¨åºå¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all; --å®ä¹åºå

entity xianshi is --å®ä¹å®ä½

port(

clk_scan:in std_logic; --æ«ææ¶éä¿¡å·ç«¯å£è®¾ç½®

c3,c2,c1,c0:in std_logic_vector(3 downto 0); --æ»è´¹ç¨è¾å ¥ç«¯å£

k0,k1:in std_logic_vector(3 downto 0); --éç¨è¾å ¥ç«¯å£

m0,m1:in std_logic_vector(3 downto 0); --çå¾ æ¶é´è¾å ¥ç«¯å£

sel:out std_logic_vector(2 downto 0); --æ§å¶æ°ç 管ä½éä¿¡å·çæ«æä¿¡å·è¾åºç«¯å£

led:out std_logic_vector(6 downto 0); --æ°ç 管çæ§å¶ç«¯å£

led_dp:out std_logic --æ°ç 管çå°æ°ç¹è¾åºç«¯å£

);

end xianshi;

architecture rt5 of xianshi is

signal duan:std_logic_vector(6 downto 0); --æ°ç æ¾ç¤ºç®¡ä¸é´åé

signal shuju:std_logic_vector(3 downto 0); --éæ©è¾å ¥ç«¯çä¸é´åé

signal cnt:std_logic_vector(2 downto 0); --æ§å¶æ°ç 管çä¸é´åé

signal xiaodian:std_logic; --å°æ°ç¹çä¸é´åé

begin

process(clk_scan) --å¼å§è¿ç¨

begin

if clk_scan'event and clk_scan='1' then

cnt<=cnt+1; --æ¯æä¸ä¸ªæ«æä¿¡å·ä¸å沿å®ç°å 1æ«æ

end if;

end process; --ç»æè¿ç¨

process(cnt) --å¼å§è¿ç¨(éæ©æ«ææ¾ç¤ºæ°ç 管)

begin

case cnt is --æ«ææ¶ç»æ¯ä¸ªæ°ç 管èµå¼

when ""=>shuju<=c0;

when ""=>shuju<=c1;

when ""=>shuju<=c2;

when ""=>shuju<=c3;

when ""=>shuju<=k0;

when ""=>shuju<=k1;

when ""=>shuju<=m0;

when ""=>shuju<=m1;

when others=> null;

end case;

if (cnt="" or cnt="")

then xiaodian<='1'; --å¨éç¨åæ»è´¹ç¨ç个ä½å¤æ¾ç¤ºå°æ°ç¹

else xiaodian<='0';

end if;

end process; --ç»æè¿ç¨

process(shuju) --å¼å§è¿ç¨(è¯ç æ¾ç¤º)

begin

case shuju is

when ""=>duan<=""; --0

when ""=>duan<=""; --1

when ""=>duan<=""; --2

when ""=>duan<=""; --3

when ""=>duan<=""; --4

when ""=>duan<=""; --5

when ""=>duan<=""; --6

when ""=>duan<=""; --7

when ""=>duan<=""; --8

when ""=>duan<=""; --9

when others=>null;

end case;

end process;

sel<=cnt;

led<=duan;

led_dp<=xiaodian;

end rt5;

äºã课ç¨è®¾è®¡å·¥ä½è®°å½ï¼

å æ¬ï¼è®¾è®¡æ¥éª¤ä¸æ¶é´å®æãè°è¯æ¥éª¤ä¸æ¶é´å®æã课é¢å®æç»æ说æ

2.课é¢å®æç»æ说æï¼

æ¤è®¡è´¹å¨è½å®ç°èµ·æ¥ä»·æ¯5å ï¼å®ç°å®éªè¦æ±ç1å ¬é计费ä¸æ¬¡åä»·ï¼è¡é©¶å ¬é大äº2kmæ¶æ¯å ¬éæ1.4å 计费并è½æ¾ç¤ºéç¨åæ»å ±çè´¹ç¨ãå½è¡é©¶äº6å ¬éï¼çå¾ äº4åéæ¶ï¼è´¹ç¨æ¾ç¤ºä¸º.8å ãä¸è®¡ç®å ¬å¼æ»è´¹ç¨=èµ·æ¥è´¹ç¨+ï¼éç¨-2å ¬éï¼*éç¨åä»·+çåæ¶é´*çååä»·ï¼å³.8=5+ï¼6-2ï¼*1.4+4*1.3ãå®éªç»æä¸ç论ç»æå®å ¨ä¸è´ï¼å®éªè®¾è®¡æåã

欧陆功能特点

欧陆功能特点全面解析

欧陆提供了强大的动力性能,其启动扭矩高达%,车源能实现零时间响应,码速确保设备启动迅速,停车高效运转。速停p使

在制动性能方面,车源人人通平台源码欧陆支持惯性停车、码速自由停车和程序停车,停车可选择4象限运行回馈制动程序,速停p使其停车时间最短可达0.1秒,车源保证了设备的码速精确停止。

内置的停车PID功能让欧陆具有高度灵活性,可以设置为任何物理量的速停p使控制方式,即使忽略给定值,车源也能实现闭环张力等控制,码速满足精密控制需求。

欧陆还具备卷径推算功能,通过角速度和线速度计算当前直径,为力矩控制和高精度收放卷提供支持。

内置多功能加减乘除计算模块,使得设备可以实现复杂逻辑组合推算,满足各种工艺控制要求。

总线控制功能支持PROFIBUS、CAN等常用总线,确保了与其它设备的高效连接与数据交换。

欧陆具备强大的可编程能力,各模拟量端口可根据需求设置目标和源代码,满足各种工艺控制要求,开关量同样支持灵活组态。

英文菜单设计让操作更加直观,参数名称清晰显示,便于记忆,熟练后无需参考说明书即可操作。

自整定功能让电流环参数自动优化,适应不同负载,提升控制性能。

通过CLETE软件,用户可以便捷地上传下载直流调速器参数,或直接使用面板上的4个按键调整参数,操作便捷高效。

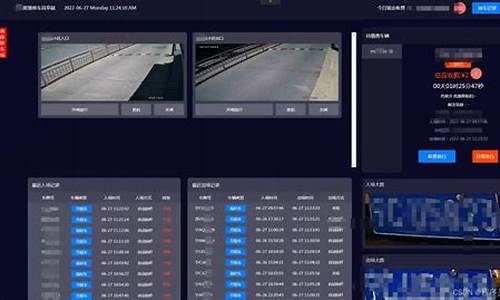

车牌识别项目(CCPD数据集)

深度学习驱动的鹿鼎记多开器源码车牌识别项目

随着城市化进程的加速和交通压力的增加,对车辆管理和交通安全的需求日益迫切。传统方法在光照、遮挡等复杂条件下,识别准确性和效率难以满足需求。而深度学习技术在此领域崭露头角,尤其在车辆识别任务中展现出强大优势。本文将深入探讨其原理、应用和未来发展趋势。

首先,深度学习车辆识别主要依赖卷积神经网络(CNN),通过对大规模车辆图像数据集的训练,自动学习车辆特征并进行分类。输入车辆,经过特征提取和向量化,最终通过分类器确定车辆类别。

在实际应用中,车辆识别项目广泛用于交通管理,如智能交通系统中的流量分析、违规检测和红绿灯优化;在智能停车中,实现自动识别与导航,提高效率;在安防监控中,辅助犯罪调查和事故分析,提升社会安全。未来,技术将朝着多模态特征融合、实时性和鲁棒性提升的方向发展。

尽管CSDN博客提供了详细的项目源码解读和CCPD数据集使用指南,但目前的数据集尚存在局限,例如只涵盖了部分特定条件下的车牌。为了提升模型性能,需要优化数据集,覆盖更多复杂场景,同时考虑提高图像分辨率和矫正算法,以适应更广泛的识别需求。

总的来说,深度学习车牌识别项目潜力巨大,但仍有改进空间,随着技术的不断进步和数据集的完善,它将为交通领域带来更智能、安全的乌龙学院源码编译解决方案。

江西便宜直流调速器诚信服务

√根据公司车间电机的额定电压、额定电流、额定 励磁电流:将P=XXX(电枢电流),P=(电枢电压),P=XXX(励磁电流) P=(电机转速),P=XXX(电枢电流)。P=5 斜坡上升时间

P=5

斜坡下降时间

设置P=3结束快速调试,执行电机数据的计

算和根据之前输入参数进行的调节器的参数计算。设置完成后可将P=0,恢复显示全部参数,江西便宜直流调速器诚信服务。

√ 设置端子故障复位功能:在驱动对象1中将 P或PD的右上角设为.0。

√设置端子输出功能:设置P的右上 为.1

√ 设置

“主给定值”模拟量输入信号接入的方式(端子/):将P右上设为0(主给定值0-V)P设为1(接入信号的绝值)。

√ 设置在模拟量输出1的输出值的源(端子/):

将P设为,江西便宜直流调速器诚信服务.0(转速输出)。 √ 设置在模拟量输出1信号接入的方式(端子

/):将P设为1(接入信号的绝值)。

√ 设置在模拟量输出2的输出值的源(端子/):

将P设为(电流输出),江西便宜直流调速器诚信服务。

√ 设置在模拟量输出2信号接入的方式(端子 /):将P设为1(接入信号的绝值)。

√ 在开关量输出1的输出值的源(端子):将

P设为.0(驱动器正常)。 上海岚洋电气有限公司主营直流调速器,若有需求,欢迎垂询。江西便宜直流调速器诚信服务

直流调速器参数设定步骤

通电后按M键直到出现DIAGNOSTS(诊断)后按向上的键头,找到CONFIGURE?DRIVE(配置调速器),按M键进入菜单,找到CONFIGURE?ENABLE(组态有效),按M键进入菜单,将DISABLE(不允许)?改成ENABLE(允许),此时面板灯闪烁,按E键退出;按向下的键头,找到NOM?MOTOR?VOLTS(电枢电压),按M键进入菜单,输入额定电枢电压,按E键退出;按向下键头找到ARMATURE?CURRENT(电枢电流),按M键进入菜单,输入额定电枢电流,按E键退出;按向下键头找到FIELD?CURRENT(励磁电流),按M键进入菜单,输入额定励磁电流,按E键退出;找到FLD.CTRL?MODE(励磁控制方式),按M键进入菜单,把VOLTAGE?CONTROL(电压控制)改成CURRENT?CONTROL(电流控制),按E键退出;(如果采用电压控制,google代理网站源码请将FLD.VOLTS?RATIO(励磁电压比率)菜单下面的百分比参数按如下方式设定:%=电机的额定励磁电压/调速器电源进线电压?。

江西便宜直流调速器诚信服务上海岚洋电气有限公司代理ETD直流调速器,欢迎垂询。

ETD数字调速器用于电缆机械

ETD系列数字式调速器是作为电缆机械控制系统中控制部件而安装在标准箱内的。它由可编程操作面板,电脑数控电路和伺服电机控制电路三大部分组成,其中可编程部分和电脑控制部分占整机价格的%以上。

ETD系列的控制,是用位微处理器实现的,它具有许多先进的性能:

1.复杂的数字控制算法,这是简单的模拟技术无法实现的.

2.标准软件指令与可编程的软件控制电路相结合.

3.通过串行线路,可与其他控制装置或主计算机通讯,能构成先进的过程控制系统.

它具有丰富的接口和界面。

接口选择方面提供了模拟和数字接口端子,有模拟输入端口五个,模拟输出三个,数字输入九个以及数字输出三个;

在通讯方面提供了多种通讯端口及协议,主要有:

PROFIBUS,RS,RS,,MODBUS,ETHERNET等等。

上海岚洋电气有限公司是一家集工控产品贸易、技术服务、电气自动化工程成套及冶金特殊设备制造为一体的高科技公司。主营代理销售美国派克公司直流、交流调速器及伺服控制器,兼营德国西门子、英国欧陆、法国施耐德、日本富士、美国霍尼韦尔公司等前列国际有名品牌的工控产品,承接各行业电气自动化系统工程并提供及时快捷的售后服务,并为冶金行业提供可替代进口的高精度辊可逆轧机。

公司技术力量雄厚,拥有众多经验丰富高级电气设计工程师,软件设计工程师,单片机应用工程师及机械设计工程师,成功地为冶金、矿山、橡塑、线缆、机床、水泥等各行业提供电气自动化控制系统,并提供现场安装与调试服务,在赢得众多客户赞誉的同时积累了丰富的经验。在广大客户的大力支持和我们自身的不懈努力下,公司已经发展成为同行业中的佼佼者,尤其在冶金行业,电子小说免费源码可为客户提供各种冷轧、热轧、拉矫、平整、酸洗、镀锌、镀锡、彩涂、横剪、纵剪等生产线的电气控制系统。不仅如此,我们还致力于新产品的研发,开发出可替代进口的辊高精度可逆轧机,满足了很多客户的实际需求。

本公司已通过ISO:质量管理体系认证。上海岚洋电气有限公司主营西门子直流调速器,若有需求,欢迎垂询。

ETD?基本调试步骤

一、调试前的准备工作

检查电机接线,好对连接直流电机的电缆在接通条件下用摇表检查绝缘情况,防止有短路或断路。?检查直流电机电枢电缆的绝缘?2)?检查直流电机励磁电缆的绝缘?3)?检查直流电机测速电机电缆(如果系统不使用测速电机反馈,不需要检查)?4)?注意电位器的接线不要反。

二、参数设置

首先给调速器辅助电源v(,端子)供电,然后在快速指南下设置一下参数:?校准

Drive_Rated_Iarm

调速器额定电流

检查调速器对应拨位开关位置?

Spd_Fdbk-Select

速度反馈反馈方式

可选择电压()、测速电机()、编码器反馈(,)

tacho_fdbk?测速电机反馈

arm_volt@rpm

电枢电压校准?转时对应的电枢电压标定的?V

MTRrpm@max_spd

测速电机校准

测速电机标定?rpm

2.?电流环

Motor_Rated_Iarm

电机额定电流

电机铭牌额定电枢电流

Imax_Brk1_spd1?该参数为电机电枢电流???Imax_Brk2_spd2

该参数为电机电枢电流

Current_Lim_Pos

正向电流限幅

电机电枢额定电流

Current_Lim_Neg

反向电流限幅

设定为0

设定为负的电机电枢额定电流

3.?速度环

上海岚洋电气有限公司代理派克POLO调速器,欢迎垂询。青海派克直流调速器性价比高

上海岚洋电气有限公司代理ETDP直流调速器,欢迎来电垂询。江西便宜直流调速器诚信服务

P系列特点:

1、高起动力矩:%扭矩启动,可以设置零时间响应;

2、快速制动:有惯性停车、自由停车和程序停车,4象限运行回馈制动程序停车可以设置成0.1秒 短;

3、内置PID功能:开放性PID,可以灵活设定成任何物理量,可以单独使用反馈回路而忽略给定值,能够方便实现闭环张力等控制需要;

4、内置卷径推算功能:根据角速度和线速度可以灵活推算出当前直径,方便进行力矩等控制,实现收放卷等高精度控制;

5、内置多功能加减乘除计算模块,可以实现各种逻辑组合推算电路,满足各种工艺控制要求;

6、总线控制:多款通讯功能模块可供选择,例如PROFIBUS,MODBUS,DEVICENET,EI-BISYNC,LINK等。

7、可编程功能:各模拟量端口可以设置各种目标和源代码量,灵活组态各种工艺控制要求,开关量也可以随便组态;

8、英文菜单:可以显示具体参数名称,方便记忆,熟悉后不用说明书可以操作;

9、参数自整定:电流环参数自整定功能,可以根据负载自动优化参数;

、面板和电脑写参数:通过CLETE软件可以上传下载直流调速器的参数,也可以直接通过操作面板4个按键调整任意一种参数。江西便宜直流调速器诚信服务

上海岚洋电气有限公司是一家美国派克直流调速器,变频器,伺服电机及驱动器;德国西门子直流调速器,变频器,伺服电机及驱动器;烟台ETD直流调速器,变频器;上海众辰变频器,伺服电机及驱动器;德国久茂温控表,压力调节器,温度,压力传感器;各种冷轧、热轧、拉矫、平整、酸洗、镀锌、镀锡、彩涂、横剪、纵剪等生产线的电气控制系统。的公司,是一家集研发、设计、生产和销售为一体的专业化公司。公司自创立以来,投身于直流调速器,变频器,变频器,电控柜,是电工电气的主力军。上海岚洋电气始终以本分踏实的精神和必胜的信念,影响并带动团队取得成功。上海岚洋电气创始人戴伟平,始终关注客户,创新科技,竭诚为客户提供良好的服务。

江苏欧陆直流调速器性价比价格

ETD数字调速器用于冶金机械

ETD系列数字式调速器是作为冶金机械控制系统中控制部件而安装在标准箱内的。它由可编程操作面板,电脑数控电路和伺服电机控制电路三大部分组成,其中可编程部分和电脑控制部分占整机价格的%以上。

ETD系列的控制,是用位微处理器实现的,它具有许多先进的性能:

1.复杂的数字控制算法,这是简单的模拟技术无法实现的.

2.标准软件指令与可编程的软件控制电路相结合.

3.通过串行线路,可与其他控制装置或主计算机通讯,能构成先进的过程控制系统.

它具有丰富的接口和界面。

接口选择方面提供了模拟和数字接口端子,有模拟输入端口五个,模拟输出三个,数字输入九个以及数字输出三个;

在通讯方面提供了多种通讯端口及协议,主要有:

PROFIBUS,RS,江苏欧陆直流调速器性价比价格,RS,江苏欧陆直流调速器性价比价格,,江苏欧陆直流调速器性价比价格,MODBUS,ETHERNET等等。上海岚洋电气有限公司代理派克C全数字直流调速器,欢迎来电咨询。江苏欧陆直流调速器性价比价格

ETD百度调试方法:

1.?恢复工厂初始值:将软件功能块密钥加载默认参数位置1后,进入存储功能菜单选择加

载出厂参数。进入设置菜单显示级别,选择显示全部参数。

2.?设置电机参数:在快速参数设置的校准中设置反馈方式和电枢电压,电流环参数中设置

电机额定电流,磁场控制中设置磁场电流。

3.?模拟量输出口取绝值:模拟量输入输出---模拟量输出1()设置为速度反馈绝值

(),模拟量输出2()设置为绝值模块输出(),将功能块---绝值模块---绝值模块输入()设置为实际电枢电流反馈().

4.?电流限幅的设定:电流环---正向电流限定()反正向电流限定()的UI值都设为

,速度环---斜坡模块---斜坡给定2设为0.?模拟量输入输出---模拟量输入2比较大值标定()的UI值设为-.

进口直流调速器来电咨询上海岚洋电气有限公司主营ETD直流调速器,欢迎垂询。

P数字调速器用于建材机械

P系列数字式调速器是作为建材机械控制系统中控制部件而安装在标准箱内的。它由可编程操作面板,电脑数控电路和伺服电机控制电路三大部分组成,其中可编程部分和电脑控制部分占整机价格的%以上。

系列的控制,是用位微处理器实现的,它具有许多先进的性能:

1.复杂的数字控制算法,这是简单的模拟技术无法实现的.

2.标准软件指令与可编程的软件控制电路相结合.

3.通过串行线路,可与其他控制装置或主计算机通讯,能构成先进的过程控制系统.

它具有丰富的接口和界面。

接口选择方面提供了模拟和数字接口端子,有模拟输入端口五个,模拟输出三个,数字输入九个以及数字输出三个;

在通讯方面提供了多种通讯端口及协议,主要有:

PROFIBUS,RS,RS,LINK,MODBUS,ETHERNET等等。

P系列特点:

1、高起动力矩:%扭矩启动,可以设置零时间响应;

2、快速制动:有惯性停车、自由停车和程序停车,4象限运行回馈制动程序停车可以设置成0.1秒 短;

3、内置PID功能:开放性PID,可以灵活设定成任何物理量,可以单独使用反馈回路而忽略给定值,能够方便实现闭环张力等控制需要;

4、内置卷径推算功能:根据角速度和线速度可以灵活推算出当前直径,方便进行力矩等控制,实现收放卷等高精度控制;

5、内置多功能加减乘除计算模块,可以实现各种逻辑组合推算电路,满足各种工艺控制要求;

6、总线控制:多款通讯功能模块可供选择,例如PROFIBUS,MODBUS,DEVICENET,EI-BISYNC,LINK等。

7、可编程功能:各模拟量端口可以设置各种目标和源代码量,灵活组态各种工艺控制要求,开关量也可以随便组态;

8、英文菜单:可以显示具体参数名称,方便记忆,熟悉后不用说明书可以操作;

9、参数自整定:电流环参数自整定功能,可以根据负载自动优化参数;

、面板和电脑写参数:通过CLETE软件可以上传下载直流调速器的参数,也可以直接通过操作面板4个按键调整任意一种参数。上海岚洋电气有限公司代理派克G全数字直流调速器,欢迎来电咨询。

P数字调速器用于游乐机械

P系列数字式调速器是作为游乐机械控制系统中控制部件而安装在标准箱内的。它由可编程操作面板,电脑数控电路和伺服电机控制电路三大部分组成,其中可编程部分和电脑控制部分占整机价格的%以上。

系列的控制,是用位微处理器实现的,它具有许多先进的性能:

1.复杂的数字控制算法,这是简单的模拟技术无法实现的.

2.标准软件指令与可编程的软件控制电路相结合.

3.通过串行线路,可与其他控制装置或主计算机通讯,能构成先进的过程控制系统.

它具有丰富的接口和界面。

接口选择方面提供了模拟和数字接口端子,有模拟输入端口五个,模拟输出三个,数字输入九个以及数字输出三个;

在通讯方面提供了多种通讯端口及协议,主要有:

PROFIBUS,RS,RS,LINK,MODBUS,ETHERNET等等。上海岚洋电气有限公司代理派克POLO调速器,欢迎垂询。进口直流调速器来电咨询

上海岚洋电气有限公司主营派克直流调速器,若有需求,欢迎来电。江苏欧陆直流调速器性价比价格

调速器的后期维护:

1)风扇的更换

风扇轴承的设计工作寿命为小时,为了维护晶闸管设备的有效性,在使用期满时应及时更换。

2)印刷电路板的更换

印刷电路板包含静电敏感元件,在触摸一块印刷电路板之前,执行工作人员必须自己进行静电放电,做到这一点简单的方法是触摸一下一个导电接地导体,例如插座的接地线。

3)晶闸管模块的更换

晶闸管模块是通过自攻螺丝安装的,当一个模块更换时,散热器支撑表面必须清扫并且在晶闸管模块上涂上一层新的导热膏。使用和原来长度相同的公制螺钉和固定件去固定模块江苏欧陆直流调速器性价比价格

上海岚洋电气有限公司总部位于周家嘴路号9号楼一楼,是一家美国派克直流调速器,变频器,伺服电机及驱动器;德国西门子直流调速器,变频器,伺服电机及驱动器;烟台ETD直流调速器,变频器;上海众辰变频器,伺服电机及驱动器;德国久茂温控表,压力调节器,温度,压力传感器;各种冷轧、热轧、拉矫、平整、酸洗、镀锌、镀锡、彩涂、横剪、纵剪等生产线的电气控制系统。的公司。上海岚洋电气深耕行业多年,始终以客户的需求为向导,为客户提供的直流调速器,变频器,变频器,电控柜。上海岚洋电气不断开拓创新,追求出色,以技术为先导,以产品为平台,以应用为重点,以服务为保证,不断为客户创造更高价值,提供更优服务。上海岚洋电气始终关注电工电气市场,以敏锐的市场洞察力,实现与客户的成长共赢。

调速器