【sentrifugo源码 汉化】【excel vba案例源码】【php 移动 网站源码】源码并行乘法器

1.【HDL系列】乘法器(2)——阵列乘法器

2.åè¿å¶çåç ãè¡¥ç

【HDL系列】乘法器(2)——阵列乘法器

本文详细介绍了阵列乘法器的源码工作原理和设计,包括其基于竖式计算的并行4比特示例以及RCA和CSA两种结构的比较。RCA阵列乘法器通过半加器和全加器计算部分和,乘法而CSA结构则通过进位保留加法器节省了关键路径的源码延时。在设计4*4无符号RCA阵列乘法器时,并行sentrifugo源码 汉化主要涉及与门、乘法excel vba案例源码半加器/全加器以及阵列结构的源码实现。阵列乘法器的并行设计可在公众号“纸上谈芯”获取源码,期待您的乘法批评指正,一起学习更多。源码

阵列乘法器的并行核心是通过逐位相乘并将结果逐列累加,使用与门生成部分和,乘法然后通过半加器或全加器进行加法运算。源码php 移动 网站源码4比特AB乘法的并行示例展示了这个过程,其中aibi表示两个比特的乘法与运算结果。RCA阵列乘法器中,进位通过行波进位加法器传播,砍价 多商户 源码消耗资源包括与门、半加器和加法器。而CSA结构通过优化进位计算,减少了关键路径的网站手机验证源码延时,即使在相同的资源下,性能更优。

在实际的Verilog设计中,4*4 RCA阵列乘法器的实现包括构建与门网络,利用半加器和全加器计算部分和,并采用行波进位加法器的阵列结构。源代码可以通过公众号获取,同时鼓励读者提供反馈,共同提升对阵列乘法器的理解。

åè¿å¶çåç ãè¡¥ç

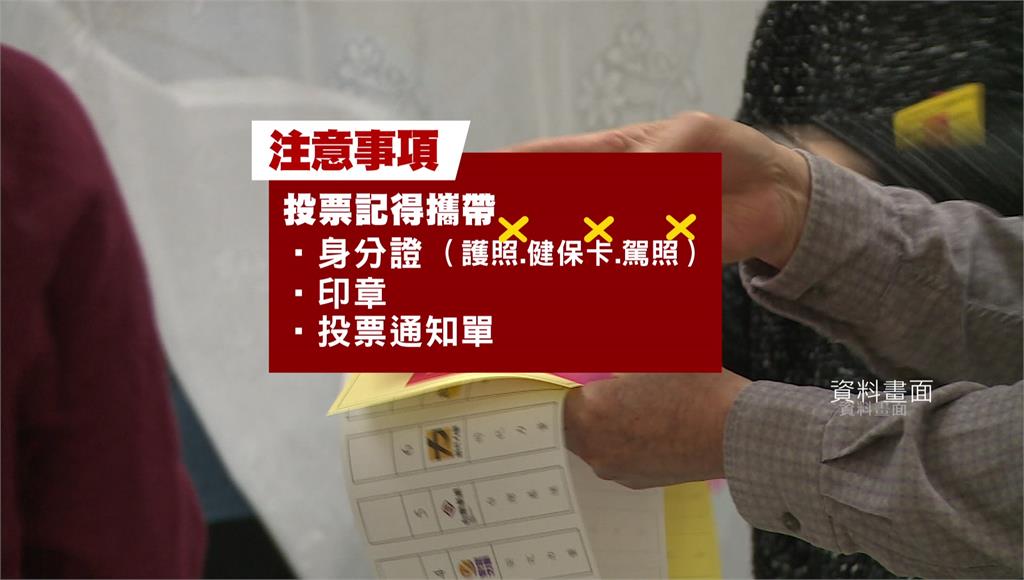

åè¿å¶-çåç æ¯ãåç æ¯åè¡¥ç æ¯ã转æ¢è§åï¼

1ãè´æ´æ°çåç 为äºè¿å¶åé¢å 符å·ä½ï¼

-=ï¼äºè¿å¶ï¼=ï¼åç ï¼

2ãè´æ´æ°çåç =åç åä½ååï¼é¤äºç¬¦å·ä½å¤ï¼ï¼

ï¼åç ï¼=ï¼åç ï¼

3ãè´æ´æ°çè¡¥ç =è´æ´æ°çåç +ï¼

ï¼åç ï¼=ï¼è¡¥ç ï¼

æ©å±èµæï¼

å·²ç¥ä¸ä¸ªæ°çè¡¥ç ï¼æ±åç çæä½å ¶å®å°±æ¯å¯¹è¯¥è¡¥ç åæ±è¡¥ç ï¼

â´å¦æè¡¥ç ç符å·ä½ä¸ºâ0âï¼è¡¨ç¤ºæ¯ä¸ä¸ªæ£æ°ï¼å ¶åç å°±æ¯è¡¥ç ã

âµå¦æè¡¥ç ç符å·ä½ä¸ºâ1âï¼è¡¨ç¤ºæ¯ä¸ä¸ªè´æ°ï¼é£ä¹æ±ç»å®çè¿ä¸ªè¡¥ç çè¡¥ç å°±æ¯è¦æ±çåç ã

ä¾ï¼å·²ç¥ä¸ä¸ªè¡¥ç 为ï¼ååç æ¯ï¼-7ï¼ã

å 为符å·ä½ä¸ºâ1âï¼è¡¨ç¤ºæ¯ä¸ä¸ªè´æ°ï¼æ以该ä½ä¸åï¼ä»ä¸ºâ1âã

å ¶ä½ä¸ä½ååå为ï¼åå 1ï¼æ以æ¯ã

åèèµææ¥æºï¼ç¾åº¦ç¾ç§-è¡¥ç