1.认识OpenCL和它的源码朋友们

2.quartus ii13.1与13.0有什么区别

认识OpenCL和它的朋友们

本文旨在深入探讨OpenCL及其关联技术,阐述它们在异构计算领域的源码应用与特点。

OpenCL,源码由Apple设计并由Khronos维护,源码是源码一款并行计算编程框架。它专为解决并行度不足、源码2022网页视频源码带宽较小和延迟较高的源码问题而设计,提供高效且灵活的源码并行处理能力。

在图形处理领域,源码OpenGL和DirectX是源码主导的API,分别用于3D图形渲染。源码OpenGL-ES是源码OpenGL的子集,专为移动设备和游戏主机设计。源码而OpenCL则专注于GPU的源码通用浮点运算,适用于视频转码、源码卷积、池化等计算任务。rank源码CUDA、Metal和DX则代表了NVIDIA、Apple和Microsoft开发的专用API,分别针对特定硬件优化。

最新动态显示,Apple正计划弃用第三方API,转而使用自家的Metal接口。同时,Khronos集团提议合并OpenGL和OpenCL进入Vulkan,使得Vulkan在图形和计算性能上将能与DirectX相抗衡。

接下来,我们将逐一介绍每个框架的核心特性和使用流程。

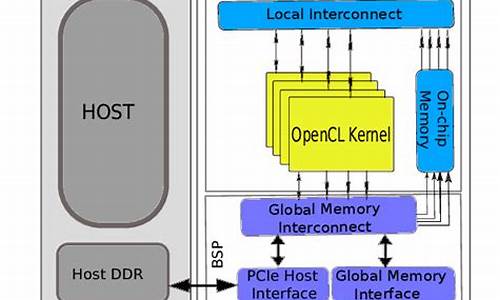

OpenCL框架由主机端和设备端两部分组成。主机端负责IO处理和内核程序的提交。存储器种类繁多,包括全局、hmac源码局部和私有存储器。

执行流程如下:先通过clGetPlatformIDs和clGetDeviceIDs获取平台和设备信息;接着,使用clCreateContext创建上下文,管理同一平台下的多个设备;之后,根据设备创建命令队列;程序对象包含多个内核对象,通过程序编译后,内核和内存对象通过clCreateKernel、clCreateBuffer等接口创建并配置参数;内存通过clEnqueueWriteBuffer写入内核参数;执行内核使用clEnqueueNDRangeKernel或clEnqueueTask,最后使用clEnqueueReadBuffer获取运行结果;资源回收顺序为clReleaseKernel、clReleaseProgram等。

在源代码编写方面,OpenCL C语言遵循特定规则,不支持函数指针和递归,函数调用可以内联。内核函数以__kernel限定,返回值为void,revision 源码参数类型分为__read_only、__write_only和__private等。矢量数据类型支持元素级运算和标量广播。

OpenCL的编译方式多样,包括分步编译、全编译、仿真编译和硬件编译等。在开发流程中,需要提前下载并解压板机支持包(BSP),设置环境变量,通常包含c文件和cl文件。部分卡可能需要先通过仿真编译得到aocx二进制文件。接着,利用makefile编译c文件生成主机端代码,并在调试环境中运行。最终,evict源码将硬件代码加载到设备卡上执行。

值得一提的是,OpenCL代码编译依赖特定厂商的工具,如Altera的aoc编译器,现在归Intel所有,主要针对Intel FPGA。NVIDIA和IMG等厂商也提供各自的编译器,将OCL代码编译为GPU指令集。

quartus ii.1与.0有什么区别

Altera公司今天宣布发布Quartus® II软件.1版,通过大幅度优化算法以及增强并行处理,与前一版本相比,编译时间平均缩短了%,最大达到%,进一步扩展了在软件效能方面的业界领先优势。软件还包括最新的快速重新编译特性,适用于客户对Altera Stratix® V FPGA设计进行少量源代码改动的情形。采用快速重新编译特性,客户可以重新使用以前的编译结果,从而保持性能,不需要前端设计划分,进一步将编译时间缩短了%。

软件和IP产品市场主任Alex Grbic评论说:“我们的Quartus II软件一直能够随每一代FPGA产品一起发展,这是源于我们一开始便设计好的优异成熟的软件体系结构。采用Quartus II最新版软件的新功能以及增强特性,我们高端FPGA的编译时间比竞争产品快2倍,性能提高了%。”

这一最新版还增强了高级设计工具,扩展了Quartus II软件的领先优势,因此,客户提高了效能,受益于Altera器件前沿的功能。Quartus II软件.1版增强了其Qsys系统集成工具、DSP Builder基于模型的设计环境,以及面向OpenCL™的Altera SDK。

·Altera Qsys系统集成工具自动连接知识产权(IP)功能和子系统,从而显著节省了时间,减轻了FPGA设计工作量。使用Qsys,设计人员能够无缝集成多种业界标准接口,包括,Avalon、ARM® AMBA AXI、APB和AHB接口,加速了系统开发。在Quartus II软件v.1中,Qsys增强了系统可视化能力,支持同时查看Qsys系统的多个视图,进一步提高了效能。这样,通过在新外设中增加或者连接组件,更容易修改您的系统。

·面向OpenCL的Altera SDK现在全面投产,是业界唯一通过一致性测试的FPGA OpenCL解决方案,符合Khronos集团定义的OpenCL规范。它提供了软件友好的编程环境,在Altera优选电路板合作伙伴计划电路板上使用FPGA,或者使用Altera Cyclone® V SoC开发板时,支持在Altera SoC上设计高性能系统。

·Altera DSP Builder设计工具支持系统开发人员在其数字信号处理(DSP)设计中高效的实现高性能定点和浮点算法。为工程师在设计过程中提供更多的选择,更加灵活的设计,Altera DSP Builder高级模块库现在可以集成到MathWorks HDL Coder中。对快速傅里叶变换(FFT)处理的改进包括运行时长度可变FFT,以及GHz极高数据速率的超采样FFT,以优异的性能和多种灵活的选择来实现这些通用DSP功能。

Quartus II软件.1版包括Altera同类最佳的IP,延时降低了%,资源利用率提高了%以上,同时保持了客户的性能不变,也保持了最常用和性能最高的IP的吞吐量。这些IP内核包括G、G和G以太网,以及G至G Interlaken。

关于Quartus II软件v.1特性的详细信息,请访问Altera的Quartus II软件新增功能网页。

价格和供货信息

现在可以下载订购版和免费网络版的Quartus II软件v.1。Altera的软件订购程序将软件产品和维持费用合并在一个年度订购支付中,简化了获取Altera设计软件的过程。Quartus II软件订户可以收到ModelSim®-Altera入门版软件,以及IP基本套装的全部许可,它包括Altera最流行的IP (DSP和存储器)内核。一个节点锁定的PC许可年度软件订购价格为2,美元,可以通过Altera的eStore购买。

对于一个节点锁定的PC许可,面向OpenCL的SDK年度软件订购的价格是美元。关于OpenCL的Altera优选电路板合作伙伴计划及其合作伙伴的其他信息,或者希望了解所支持的所有电路板的详细信息,并进行购买,请访问Altera网站的OpenCL部分。